## MPF-I

EXPERIMENT MANUAL (SOFTWARE/HARDWARE)

# MPF-IP EXPERIMENT MANUAL (SOFTWARE/HARDWARE)

#### COPYRIGHT

Copyright © 1983 by MULTITECH INDUSTRIAL CORP, All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of MULTITECH INDUSTRIAL CORP.

#### DISCLAIMER

MULTITECH INDUSTRIAL CORP. makes no representations or warranties, either express or implied, with respect to the contents hereof and specifically disclaims any warranties or merchantability or fitness for any particular purpose. MULTITECH INDUSTRIAL CORP, software described in this manual is sold or licensed "as is". Should the programs prove defective following their purchase, the buyer (and not MULTITECH INDUSTRIAL CORP., its distributor, or its dealer) assumes the entire cost of all necessary servicing, repair, and any incidental or consequential damages resulting from any defect in the software. Further, MULTITECH INDUSTRIAL CORP. reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of MULTITECH INDUSTRIAL CORP. to notify any person of such revision or changes.

OFFICE/

9FL 268 SUNG CHIANG ROAD, TAIPEI 104.

TAIWAN, R.O.C.

TEL: (02)553-1101

TELEX: 1912 MULTINC FAX: (02)542-2805

FACTORY/

1 INDUSTRYE, ROAD, III,

HSINCHU SCIENCE-BASED INDUSTRIAL PARK,

HSINCHU TAIWAN 300. R.O.C.

#### MPF-IP EXPERIMENT MANUAL

#### **TABLE OF CONTENTS**

| Preparation  |    |                                                                   |     |

|--------------|----|-------------------------------------------------------------------|-----|

|              |    | Designing Microcomputer Programs                                  |     |

|              |    | Data-Transfer Experiment                                          |     |

| Experiment   |    | Basic Applications of Arithmetic and Logic Operation Instructions |     |

| Experiment   | 3  | Binary Addition and Subtraction                                   |     |

| Experiment   | 4  | Branch Instructions and Program Loops                             | 2   |

| Experiment   | 5  | Stack and Subroutines                                             | 3.0 |

| Experiment   | 6  | Rotate, Shift Instructions, and Multiplication Routines           | 36  |

| Experiment . | 7  | Binary Division Routine                                           | 4:  |

|              |    | Binary-to-BCD Conversion Program                                  |     |

| Experiment   | 9  | BCD-to-Binary Conversion Program                                  | 5.2 |

| Experiment   | 10 | Square-Rooot Program                                              | 58  |

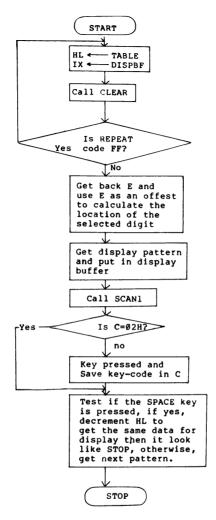

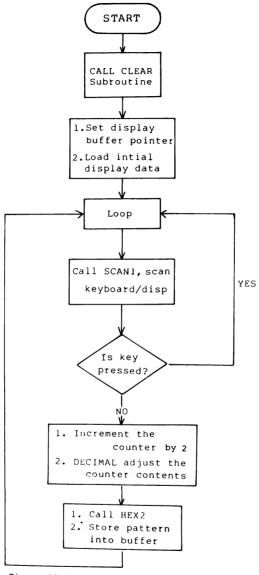

| Experiment   | 11 | Introduction to MPF-IP Display                                    | 65  |

| Experiment   | 12 | Fire-Loop Game                                                    | 71  |

| Experiment   | 13 | Stop-Watch                                                        | 76  |

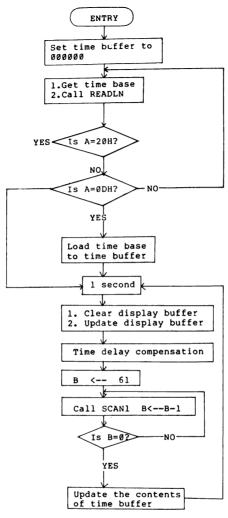

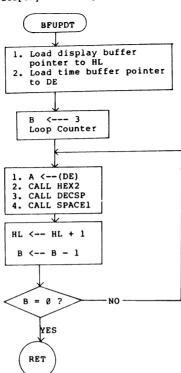

| Experiment   | 14 | Designing a Clock Using Software                                  | 90  |

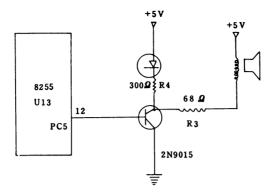

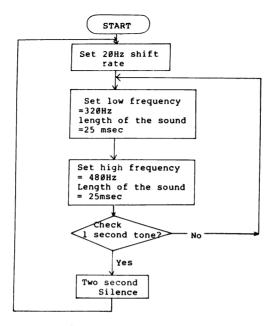

| Experiment   | 15 | Telephone Tone Simulation                                         | 97  |

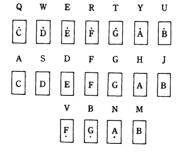

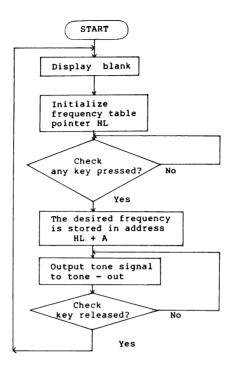

| Experiment   | 16 | Microcomputer Organ                                               | 01  |

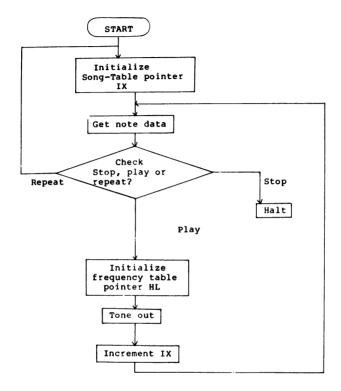

| Experiment   | 17 | Music Box Simulation                                              | 21  |

| LAPCIIIICIII |    | Masic Dox Circulation                                             | 96  |

Introduction to Designing Microcomputer Programs

A computer program is an organized series of instructions. The central processing unit will perform a series of logical actions to obtain the desired result.

Before a program is executed by CPU it must be stored in memory in binary form. This type of program is called a "machine language program". This is the only type of language the computer understands. The machine language program is usually represented by Hexadecimal digits. For example, the 8-bit instruction 1010 1111B (B represents binary ) in the Z80 CPU it can be replaced by 0AFH ( H represents hexadecimal). Interpreting a machine language program is extremely difficult and time consuming for the user. the microprocessor manufacturer divides the CPU instructions into several categories according to their functions. The CPU instructions and registers are usually represented by symbols called "mnemonics". For example, the Z80 CPU instruction 70H can be represented by the mnemonic code LD A,L (Load Data into register a from register L). A program written in mnemonic codes is called an "assembly language program." Before an assembly language program can be executed by the CPU, it must be translated into machine language by a special software program called an "Assembler".

Normally a program is written in assembly language. The main advantage of assembly language program over machine language programming is that assembly language programming is much faster to code, the mnemonics makes it much easier for the user to remember the instruction set, and normally the assembler will contain a self-diagnostic package for debugging programs. The main disadvantage of assembly language programs is that it requires an assembler and microcomputer development system. these two items are very costly. With the MPF-IP microcomputer the user has to translate assembly programs into machine level programs by hand before executing programs.

#### A. Problem Analysis

The software program of a simple problem may be easily designed with a well-defined flowchart. It may also be obtained by revising some existing programs or combining some simple routines. The design of a more complicated programs, such as monitor programs, system control programs or a special purpose program, are usually started after some detailed analysis of the problem has been made. Problem analysis and solution requires a good understanding of the following:

#### See page (III-3)

- ( 1) Characteristic and requirements of the problem

- (2) Conditions which are known

- ( 3) Input information format and how it is converted

- (4) Output data format and how it is converted

- (5) Type of data and how precise it is

- (6) Execution speed required

- (7) CPU instructions and performance

- (8) Memory size

- (9) The possibility that the problem can be solved

- (10) Methods to solve the problem

- (11) Evaluation of the program

- (12) How the resultant program will be disposed

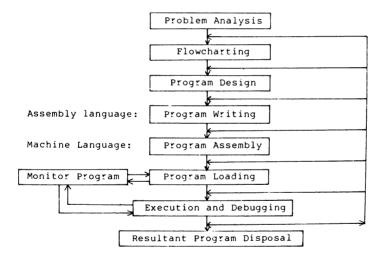

Figure A-1

#### B. Flowchart

A flowchart can be used to indicate the behavior of algorithms by suitable graphs. Once the complete flowchart has been completed, a full picture of the programmer's thought processes in reaching a solution to the problem may be followed. Flowcharts are especially important in program-debugging. It is an important part of the finished program. It may help other people to understand the exact algorithm used by the programmer.

Two levels of flowcharts are often desirable:

System flowchart -- showing the general flow of the program

Detailed flowchart -- providing details that are of interest mainly to the programmer.

Usually, a complicated program is introduced using a system flowchart outlining the program, and then a detailed flowchart is presented. The advantage of a flowchart is that it emphasizes the sequential nature of steps by using arrows pointing from each step to its successor. Various symbols are used to indicate the operation that is to be performed at each step. Figure 2-A-2 gives some standard symbols used in flowcharts:

Figure A-2

#### C. Program Design

There are many types of programs. Programs for mathematical equations, conversion of input and output signals, coding and decoding of the program data, peripheral device drives, etc. are example of simple programs. Assembler, monitor and system control programs or special purpose applications are examples of more complicated programs. The following items are usually considered in program design:

- (1) Acquisition of input signals or data

- (2) Generation or conversion of output signals and data

- (3) Logical analysis and calculations in the main program

- (4) Relation between the main program and subroutines

- (5) Use of internal registers

- (6) Memory allocation of the main program

- (7) Memory allocation of subroutines

- (8) Memory allocation of data tables and indexed addressing methods

- (9) System initialization and constants in the program

- (10) Definition of the variables in the program

- (11) Consideration of timing sequences and program execution speed

- (12) Limitations of memory size

- (13) Length and precision of data

- (14) Availability of documents and references

- (15) Other special items

#### D. Program Writing

In this book, the programs are written mainly in assembly language. Here only the format of the assembly language program is given.

A statement in the program is composed of four parts : Label, Opcode, Operand and Comment. An example is shown below

| LABEL | OPCODE  | & OPERAND  | COMMENT                                      |

|-------|---------|------------|----------------------------------------------|

|       |         |            |                                              |

| DTB4  | LD      | В,16       |                                              |

| DB3   | SRL     | Н          |                                              |

|       | RR      | L          |                                              |

|       | RR      | D          |                                              |

|       | RR      | E          | ; ROTATE HL DE RIGHT                         |

|       | LD      | A,H        |                                              |

|       | CALL    | DB1        |                                              |

|       |         | н, А       | ; CORRECT H                                  |

|       | LD      |            |                                              |

|       | CALL    |            |                                              |

|       | LD      |            | ; BINARY CORRECT L                           |

|       |         | DB3        |                                              |

|       | RET     |            |                                              |

| BINAF | Y CORRE | CT ROUTINE |                                              |

| DB4   | BIT     | 7,A        |                                              |

|       | JR      | Z,DB1      | ; IF BIT 7 OF $A = 1$ , SUB FROM 30H         |

|       | SUB     | 30H        |                                              |

| DB1   | віт     | 3,A        |                                              |

|       | JR      | Z,DB2      | ; IF BIT 3 OF A = 1, SUB FROM $\emptyset$ 3H |

|       | SUB     | 3          |                                              |

| DB2   | RET     |            |                                              |

Sometimes, a program statement without a comment is not easy to understand. The comments in the statements are very important especially for a complicated program. Statements with a label and comment field are more convenient for calling and debugging.

#### E. Program Assembly

Using the resident assembler in a microcomputer system is an effective way to assemble the source program. However, a beginner or a proram designer not familiar with the microcomputer development system must assemble his/her program by hand. The usual procedure for hand assembly is:

- (1) Translate each instruction (mnemonic) into the machine code by looking it up in the conversion table. The comment field of each statement is ignored.

- (2) After deciding the starting address of the program. Assign an appropriate address to the first byte of each instruction. The exact number of bytes needed must be reserved including space for instructions such as JR, DJNZ, and destination addresses of instructions JP, CALL, etc.

- (3) Calculate the relative displacement and put it in the assembled program. A simple formula for calculating the relative displacement is:

displacement = (destination address) - (next instruction address)

If the calculated result is positive, then it is the desired value. If the calculated result is negative, then subtract the result from 100H (i.e. take its 2's complement) and the final result is taken as the operand of this instruction. For instance, in the program listed above, the instruction DJNZ DB3 at address 0014H is first translated into 10xx and then the xx value is calculated.

- xx = 0002H (destination address) 1016H (next instruction's address)

= -14H (negative value)

- xx = 100H 14H = 0ECH

Therefore, the instruction DJNZ DB3 must be translated into 10EC. In addition, the instruction JR Z, DB l at address 0019H is first translated into 28xx, and then the xx value is calculated.

xx = 001DH (destination address) - 001BH (next instruction's address) = 2 H

The instruction JR Z, DB 1 must be translated into 2802.

The translated machine language is given below:

#### Machine Address Language Label Opcode & Operand Comment ------; \*\* 4 DIGIT BCD TO BINARY CONVERTION ROUTINE \*\* ; EXTRY : BCD DATA IN HL ; EXIT : BINARY DATA IN DE ; REGISTER CHANGED : AF BC DE HL 0000 0610 DTB4 LD B.16 ; B = BIT COUNT0002 CB3C DB3 SRI. н

```

0004

CB1D

RR

L

RR

D

0006

CBlA

0008

CB1B

RR

E

; ROTATE HL DE RIGHT

aaaa

7C

LD

A,H

000B

CD1D00

CALL

DB1

. 67

LD

000E

H,A

; CORRECT H

7D

LD

000F

A.L

0010

CD1700

CALL

DB4

0013

6F

LD

L,A

; BINARY CORRECT L

0014

10EC

DJNZ

DB3

C9

RET

0016

; BINARY CORRECT ROUNTINE

0017

DB4

віт

CB7F

7,A

0019

2802

JR

Z,DBl

; IF BIT 7 OF A = 1, SUB FROM 30H

001B

D63Ø

SUB

3ØH

DB1

BIT

3,A

ØØ1D

CB5F

001F

2802

JR

Z,DB2

; IF BIT 3 OF A = 1, SUB FROM Ø3H

3

0021

D603

SUB

0023

C9

DB2

RET

```

### Experiment 1 Data-Transfer Experiment

#### Purposes:

- To familiarize the user with the function of data-transfer instruction

- 2. To practise setting the initial value of data

- 3. To practise assembling, loading and executing a program

#### Time required: 4 hours

- I. Theorectical Background:

- Most of the data-transfer operation is accomplished by using LD (load) instructions. Data can be transferred in group of 8 bits or 16 bits. Also, instructions such as EX, EXX, PUSH and POP can be used to transfer 16-bit data. Instructions such as LDI and LDIR can be used to transfer blocks of data by moving a series of bytes.

- 2. A LD instruction must have two operands. The first operand represents the location where data will be stored (register or memory section). This is called its "destination". The second operand represents the original location of the data to be transferred. This is called the "source". For instance, LD A,B indicates that data in register B will be transferred to register A. Register A is the "destination" and Register B is the "source".

- Data transfer instructions can be used in the following ways:

```

(1) register <- register e.g.</p>

LD A,B

: LD HL,BC

(2) register <- memory

e.g.

LD A, (HL)

; POP AF

(3) register <- immediate data

e.g.

LD A,25H

; LD HL,125AH

(4) memory <- register

LD (HL),A ; PUSH BC

e.g.

(5) memory <- memory

LDD

: LDIR

```

(5) memory <- memory e.g. LDD ; L (6) memory <- immediate data e.g. LD (HL),5BH

#### II. Experiment 1-1

Write an assembly language program to set the contents of the registers as follows:  $A=\emptyset$ , B=1, C=2, D=3, E=4, H=5, L=6 (use 8-bit LD instruction to transfer one byte of data each time).

- Step 1 Write the assembly language program in the following blank form. The last instruction is RST 38H which returns control of the MPF-IP to the monitor program after executing the whole program.

- Step 2 Key in the source program using the text editor or input mchine code directly to the MPF-IP.

- Step 3 Use the two-pass assembler to assemble the source code to machine code without modifying the default values. Then key in G F B 0 0 and \_\_\_\_\_ to execute the program.

- Step 4 Examine the contents in the A, B, C, D, E, H, L registers. If the values are not stored properly, repeat from step 1.

- \* Table --- from Chinese MPF-IP Manual p.12

| Memory  | Machine  | Assembly |

|---------|----------|----------|

| Address | Language | Language |

|         |          |          |

| 1800H   | 3EØØ     | LD A,Ø   |

|         |          |          |

FF RST 38H

#### III. Experiment 1-2

Write an assembly language program to set the contents of registers as follows: B=12, C=34, D=56, E=78, H=9, L=A (use 16-bit LD instruction to transfer two bytes of data each time).

- Step 1 Same as the step 1 in Experiment 1-1.

- Step 2 Same as the step 2 in Experiment 1-1.

- Step 3 Press G F B Ø Ø and to execute the program.

- Step 4 Use the v key to check contents of each register.

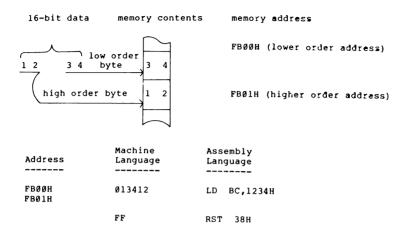

A 16-bit data is composed of two bytes of data. The high-order byte is stored in the higher ordered memory address and the low-order byte is stored in the lower ordered memory address. For instance, the 16-bit data 1234H is stored in addresses 1820H - 1821H in the following way:

Example 1-1: THE USE OF A LOOP

Write a program to clear the contents of memory addresses FA00H - FA1FH.

#### Explanation:

- (1) If we use an 8-bit LD instruction to transfer the data to each destination, the single load instruction would be executed for 32 (20H) times. It is more convenient to use the loop method in the program.

- (2) Use register B is generally used as a loop counter. Set register B to 20H before the loop is executed. Use HL as a memory address pointer, and set the starting address FA00H to HL. HL is incremented by one and B is decremented by one for each loop. If B=0, then all loops have been executed; otherwise, run the loop again.

#### (3) The program is given below:

| Address | Machine<br>Language | Label | Opcode   | & Operand | Comment                                                                  |

|---------|---------------------|-------|----------|-----------|--------------------------------------------------------------------------|

| F800    |                     |       | LD<br>LD |           | ; Set loop counter equal to 32<br>; Set HL equal to the starting address |

|         |                     |       | XOR      | A         | ; of memory to be cleared ; Set A=0                                      |

|         |                     | LOOP  | LD       |           | ; Load Ø into the memory address ; pointed to by HL                      |

|         |                     |       | INC      | HL        | ; Increment HL by 1                                                      |

|         |                     |       | DEC      | В         | ; Decrement HL by 1                                                      |

|         |                     |       | JR       | NZ,LOOP   | ; If B not = 0, return to LOOP                                           |

|         | FF                  |       | RST      |           | ; Return to the monitor program                                          |

#### IV. Experiment 1-3

Enter the program in the Example 1-1, assemble the source code to machine code, execute the program. Then check if the contents of the memory range from FA00H through FA1FH has been cleared.

#### V. Experiment 1-4:

Write an assembly language program to set the contents of memory address FA50H - FA7FH as follows: 0, 1, 2, 3, ....F.

(HINT: Change the loop counter and the value of the starting address. register A is incremented by '1' in the next loop)

| ADDRESS | MACHINE<br>LANGUAGE | LABEL | OPCODE & OPERAND |

|---------|---------------------|-------|------------------|

|         |                     |       |                  |

|         |                     |       |                  |

|         |                     |       |                  |

|         |                     |       |                  |

|         |                     |       |                  |

## Experiment 2 Basic Applications of Arithmetic and Logic Operation Instructions

#### Purposes:

- To familiarize the user with the arithmetic and logic operation instructions

- 2. To understand the memory addressing modes

- 3. To understand the meaning of the register status flag

- 4. To practise arranging data for CPU registers and memory sections

#### Time Required: 4 hours

- I. Theoretical Background:

- 1. 8-bit arithmetic and logic operation instructions:

The 8-bit arithmetic and logic operations in the 280 CPU are performed in register A (accumulator). Registers A, B, C, D, E, H, and L can be used as operands in conjunction with register A in the LD instructions. If data are transferred between memory and register A, the memory address can be pointed to by HL, IX or IY registers. The meaning of the following instructions are given in the right-side comment field:

| (1) | ADD A    | ; | Data in register A is added to itself, i.e. the data is doubled shifted left one bit.                                             |

|-----|----------|---|-----------------------------------------------------------------------------------------------------------------------------------|

| (2) | ADC B    | ; | Register B and the carry flag are added to register $\lambda$ .                                                                   |

| (3) | SUB C    | ; | Data in register C is subtracted from register A.                                                                                 |

| (4) | SBC (HL) | ; | Subtract the data in the memory address pointed to by HL and the contents of the carry flag from register $\hbox{A.} \hskip 10pt$ |

| (5) | AND D    | ; | Logical "AND" of register D and register A.                                                                                       |

| (6) | OR ØFH   | ; | Logical "OR" of data $\emptyset$ FH and register A .                                                                              |

| (7) | XOR A    | ; | Exclusive "OR" register A and itself. (Since register A is equal to register A, the result is zero).                              |

- (8) INC H ; Increment the contents of register H by 1.

- (9) INC (IX) ; Increment the contents of the memory address pointed to by register IX by 1.

- (10) DEC C ; Decrement the contents of register C by 1.

- (11) DEC (IY+3)

- ; The sum of the contents of register IY and 3 is used as the memory address pointer. Decrement the contents of memory address IY +3.

#### 2. Data Addressing Mode

In the above assembly language instructions, the addressing modes used can be summarized below. Other addressing modes can be found in the Z80 CPU technical manual.

(1) Register Addressing

#### Example:

In the instruction ADC A,B, ADC is the opcode which represents what kind of operation will be performed. The character A in the right means that the data will be added to A. The character B at the far right means that the data to be added to A is taken from register B.

(2) Register Indirect Addressing

A 16-bit register is used to store the memory address.

Example: In the instruction SBC A,(HL), (HL) does not mean that HL will be subtracted from register A. Instead, the CPU takes the 16-bit data contained in HL as the memory address and then accesses the 8-bit data stored in this memory address. The 8-bit data pointed to by HL is finally subtracted from register A. IX and IY are called index registers. When a memory address is pointed to by IX or IY, an 8-bit byte which is less than +127 but larger than -128 can be added to this register.

For instance, the following two instructions can be used to add the data stored in the memory address pointed to by IX to the 8-bit data stored in the memory address pointed to by IX+2. The result is stored in register A.

LD A,(IX) ADD A,(IX+2)

#### (3) Immediate Addressing

Example: OR ØFH. On the right-hand side of the opcode OR, a hexadecimal number, ØFH, is given. It means that the number ØFH is logically ORed with the contents of register A. Therefore, the data is part of the instruction which is stored in memory. The CPU fetches the data by using the program counter (PC) as a reference address. The following instructions are examples of immediate addressing.

LD B,8 ADD A,44H SUB A,0A4H

#### 3. Status Flags

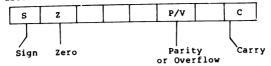

After a logical or arithmetic operation is finished, the result will be stored in register A and some of the status flags (Carry, Overflow, Change Sign, Zero Result, Parity) will also be affected. These status flags will be stored in the flip flops in the Z-80 CPU. These flip flops form a register called the Flag Register. The data in this register can be moved to memory, like data in other registers, by specific instructions (PUSH instruction). Some of the status flags are given below.

#### (1) Carry Flag

This flag is the carry from highest order bit of the Accumulator. The carry flag will be set in either a signed or unsigned addition where the result is larger than an 8-bit munber. This flag is also set if a borrow is generated during a subtraction instruction. The carry flag can be used as a condition for jump, call, or return instructions. The carry flag also serves as an important linkage in multi-byte arithmetic operations. Three 8-bit data can be connected as a 24-bit data by using carry flag and four 8-bit data can be connected as a 32-bit data.

#### (2) Overflow/Parity Flag

When signed two's complement arithmetic operations are performed, this flag represents overflow. The 2-80 overflow flag indicates that the signed two's complement number in the accumulator has exceeded the maximum possible (+127) or is less than minimum possible (-128).

When an arithmetic operation is performed in the Z80-CPU, the number in register A can be assumed to be unsigned data ( $\theta$  - 255) or signed data (-128 - +127). Thus, either the carry flag or the overflow flag can be affected by the arithmetic operation. The programmer decides which interpretation is desired. The following arithmetic operations are described on the right—hand side.

| 10101190<br>+) 11101000      | <- unsigned number 172 or signed number -84 <- unsigned number 232 or signed number -24                                    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1 <- 1001010,0               | <- unsigned number 148 with carry or signed<br>number -108 but no overflow                                                 |

| 01001010<br>+) 01000010      | <- signed or unsigned number 74<br><- signed or unsigned number 66                                                         |

| 0 <- 10001100<br>change sign | <- unsigned number 140 but no carry, or<br>signed number -116 but overflow has<br>occurred and the result becomes negative |

For logical operations in the Z80-CPU, this flag is set if the parity of the 8-bit result in the accumulator is even. This flag is very useful in checking for parity errors occurring during data transmission. Since carry and overflow will never occur in logical operations, the parity and overflow status can be stored in the same flip flop. This flip flop is called the P/V flag. By testing this flip flop the programmer can check overflow after arithmetic operations and check parity after logical operations.

#### (3) Zero Flag

If register A is zero after a logical or arithmetic operation, this status will be registered in a flip flop called zero flag. The zero flag can be used as a condition for branch instructions. It is very useful in program looping.

#### (4) Sign Flag

If the leftmost bit (bit 7) of register A is 1 after a logical or arithmetic operation, the number in register A is interpreted as a negative number. The sign flag is then set to 1. This flag will be ignored if the programmer has assigned the data as unsigned numbers.

(5) The other flags designed for BCD arithmetic are not important for the programmer. The bit positions of the flags discussed above are shown below:

In microcomputers, it is usual to represent the contents of the flag register by two hexadecimal digits. The reader reader has to express this two-digit data with an 8-bit binary number. By referring to the bit positions in the flag register, the reader can obtain the status of the flag. For instance, if the flag register is 3CH, then the sign is positive, the value is non-zero, the parity is even or there is overflow has occurred but there is no carry. To know which flags will be affected by an instruction, the reader has to refer to the assembly language manual. Not all instructions will affect the status flags.

#### II. Example of Experiments

The following program can be used to add the contents of register D and register E together. The result will be stored in the register pair HL. Load the program into MPF-IP and then execute it. Record the result.

| ORG | ØFBØØH | ; Starting Address <- 0FB00H |

|-----|--------|------------------------------|

| LD  | A,E    | ; A <- E                     |

| ADD | A,D    | ; A <- A + D                 |

| LD  | L,A    | ; L <- A                     |

| LD  | A,Ø    | ; A <- Ø                     |

| ADC | A,Ø    | ; A <- A + Ø + Carry         |

| LD  | H,A    | ; H <- A                     |

| RST | 38H    | ; Return to Monitor          |

| Preset | Value | Result o | of Program | Execut | ion |       |

|--------|-------|----------|------------|--------|-----|-------|

| Regis  | ster  | Register | ,          | Flag   |     |       |

| D      | E     | HL       | Sign       | Zero   | P/V | Carry |

| 5AH    | A6H   |          |            |        |     |       |

| 46H    | 77H   |          |            |        |     |       |

2. The following program can be used to add the 16-bit data in memory addresses FA00H - FA01H to the 16-bit value in the register pair DE. The result will be stored in the register pair HL. Load the program into MPF-IP and execute it. Discuss the result obtained.

Preset values of memory: (FAØ1H) = ,(FAØ0H) = Preset value of register DE pair = ,

| ORG                    | 0F800H                           | ; Starting address <- 0F800H                                      |

|------------------------|----------------------------------|-------------------------------------------------------------------|

| LD                     | A,(0FA00H)                       | ; A <- (FA00H)                                                    |

| ADD                    | A,E                              | ; A <- A + E                                                      |

| LD                     | L,A                              | ; L <- A                                                          |

| LD<br>ADC<br>LD<br>RST | A, (ØFAØ1H)<br>A,D<br>H,A<br>38H | ; A <- (FAØ1H) ; A <- A + D + Carry ; H <- A ; Return to monitor. |

#### Result:

| values of memory: (FAØ1H) | = ,(FAØØH)                                                   | =                                 |

|---------------------------|--------------------------------------------------------------|-----------------------------------|

| value of register DE pair | =                                                            |                                   |

| HL                        | =,                                                           |                                   |

| Carry                     | =                                                            |                                   |

| Zero                      | =                                                            |                                   |

| Overflow                  | =,                                                           |                                   |

| Sign                      | =                                                            |                                   |

|                           | value of register DE pair<br>HL<br>Carry<br>Zero<br>Overflow | value of register DE pair       = |

- 3. Revise the above program for a subtraction operation.

- 4. The following program can be used to add the 32-bit data in memory addresses @FAØ@H - @FAØ3H to the 32-bit data in memory addresses FAØ4H - @FAØ7H. The result will be stored in memory addresses @FAØ8H - @FAØBH. The higher-order byte is stored in a higher address (This is conventional in microcomputer programming)

ORG ØFBØØH LD B.4 LD IX, ØFAØØH AND Α LOOP LD A,(IX) ADC A. (IX+4) LD (IX+8),AINC ÌΧ DEC В JΡ NZ,LOOP RST 38H

| Result of program testing:    |   |                     |

|-------------------------------|---|---------------------|

| Preset memory contents:       | ( | 0FA03H - 0FA00H ) = |

|                               | ( | ØFAØ7H - FAØ4H ) =  |

| results of program execution: | ( | ØFAØBH → ØFAØ8H ) = |

|                               |   | Flag Register =     |

5. If the instruction ADC A,(IX+4) is replaced by SBC A, (IX+4), then the above program can be used for a subtraction operation. If the instruction DAA is inserted immediately after the ADC or SBC instruction, then the program becomes a program for decimal addition or subtraction. Load the revised program to MPF-IP and test it.

## Experiment 3 Binary Addition and Subtraction

#### Purposes:

- To understand how an addition or subtraction operation is performed on a microcomputer.

- To familiarize the reader with software programming techniques.

#### Time Required: 4 hours

- I. Theoretical Background:

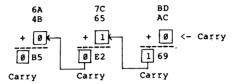

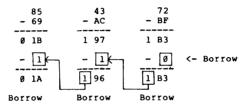

- 1. In this experiment, we only discuss unsigned binary integer addition and subtraction. For a N-bit binary number, its range is < 0,2 ±1 >. For instance, if N = 8, the range is < 0,255 >; if N = 16, the range is < 0,65535 >. If the range of the numbers are expressed by hexadecimal digits, the ranges are < 0,FFH > and < 0,FFFFH >, respectively. If the sum of an addition operation is larger than the maximum value that can be represented by N bits, then carry is generated and the carry flag is set. In the subtraction operation, if the subtrahend is more than the minuend, a borrow is generated and the carry flag is set in the high order byte. The set carry bit indicates an incorrect result.

#### Example 3-1:

Single byte addition and subtraction.

Addition: 7FH + ADH = 12CH

Carry

Subtraction: 7FH - ADH Subtraction: ADH - 7FH = 2EH

Borrow

The answer is incorrect

( CY = 1 )

Borrow

The answer is correct

( CY = 0 )

#### Example 3-2

Three-byte addition and subtraction

Addition: 6A7CBDH + 4B65ACH = B5E269H

Subtraction: 854372H - 69ACBFH =

The borrow of the highest-order byte is 0, thus the answer is correct. In multi-byte subtraction, the correctness of the result depends upon the borrow of the highest-order byte. If the borrow is 1, then the result is incorrect.

#### 2. Order of data stored in memory:

The conventional way of storing multi-byte data in memory is: the lowest order byte is stored in the lowest address and the highest order byte is stored in the highest address. The address of the multi-byte data is usually expressed by its lowest address. For beginning atstance, the number 7325H is stored beginning at memory address A in the following way:

address A

$$25$$

<- low-order byte A + 1  $73$  <- high-order byte

If the starting address of 4 three-byte numbers stored in memory is A, the data and their addresses can be shown as follows:

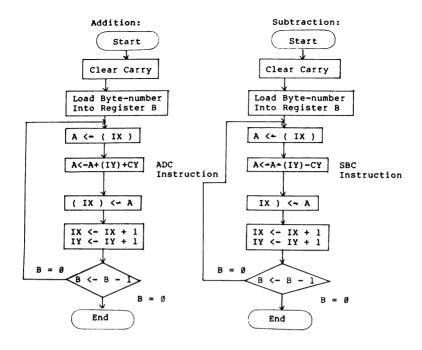

#### 3. Design of Addition/Subtraction Programs:

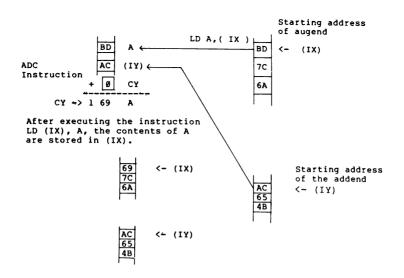

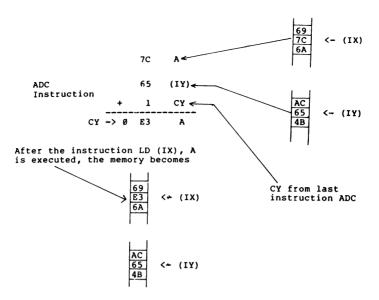

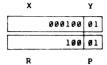

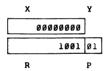

The data used in addition/subtraction operation are stored in memory according to the conventional method given above. The starting address of the augend/minuend is stored in index register IX. The starting address of addend/subtrahend is stored in index register IY. The byte-number of the data is stored in register B. First, clear CY and load the augend/ minuend into the accumulator. Then, use the indexed addressing mode instruction ADC ( SBC ) to proceed with the addition/ subtraction operation. The result is stored in the original address of the augend/minuend. Increment the index registers and compare register B with zero. Repeat the load augend, add, store increment cycle until the B register equals zero. Finally, test the carry flag to check if the result is correct. The only difference between the addition program and subtraction program is that the instruction ADC is used for addition operation and the instruction SBC is used for subtraction operation. The flowcharts and programs are given below for comparison:

The following block diagram is given to demonstrate data transfer in an addition operation.

Instruction INC IX increases the value of IX by one.

In the comment field the incrementation

of IX can be shown as IX = IX + 1

INC IY leads to IY <- IY + 1</pre>

In each of frames showing the results of an instruction step the current value pointed to by the index registers are indicated by

index register

When B =  $\emptyset$ , the program execution is completed and the memory becomes

The addition program is given below. By replacing the instruction ADC A, (IY) by SBC A, (IY), the addition program becomes a subtraction program.

```

1. *** MPF-IP EXAMPLE PROGRAM ***

2. 3-BYTE ADDITION ( UNSIGNED INTEGER )

3. ENTRY; AUGEND ADDRESS IN IX.

ADDEND ADDRESS IN IY.

5. EXIT : SUM IN AUGEND ADDRESS

7. ADD3 : XOR A ; CLEAR CARRY FLAG

8.

LD B, 3; BYTE NUMBER IN B

9. ADDLP : LD A. (IX)

10.

ADC A, (IY)

11.

LD (IX), A

INC IX

12.

13.

INC IY

14.

DJNE ADDLP

15.

RET

```

#### 4. Programming Technique:

From the above examples (3-1 and 3-2), we can see that the multibyte addition/subtraction operation can be accomplished by repeating the single-byte addition/subtraction operation, that is, by the loop operation of single-byte addition/subtraction. In the above program, register B is used as a loop counter. If the byte-number is 4, then 4 is loaded into B initially. Register B is decremented by 1 after each loop operation. The loop ends when B = 0. The instruction DJNZ is used for conditional jump. When B = 0, the program no longer executes the jump operation. Since ADC and SBC instructions are used in the programs, the CY is included in each addition/subtraction operation. Therefore, before the first byte addition/subtraction operation, the carry flag must be cleared (instruction XOR A). The index registers IX and IY are used as address pointers. By incrementing IX and IY, the CPU can access multibyte values stored in memory.

#### II. Student Exercises:

- Load the above addition program into MPF-IP and store it on magnetic tape.

- Replace the last instruction RET in the program by RST 38H. Load the following data into memory. The starting addresses of augend and addend are assigned as F900H and FA00H, respectively. Execute the program and record the result in the following table.

| Augend  | Addend  | Answer | Check |

|---------|---------|--------|-------|

| 793865H | ABCEDFH | CY =   |       |

| ØØ9543H | AB1236H | CY =   |       |

| 954717H | ØØ339ØH | CY =   | -     |

Replace the ADC instruction by the SBC instruction. Assign the starting addresses of minuend and subtrahend as F900H and FA00H, respectively. Execute the program and record the results obtained.

| Minuend | Subtrahend | Answer | Check |  |  |

|---------|------------|--------|-------|--|--|

| 683147H | 336700Н    |        |       |  |  |

| 5935ABH | 5877FFH    |        |       |  |  |

| Ø49677H | F65B79H    |        |       |  |  |

- Express the data in the above two tables as five-byte data. Change the byte-counter to the proper value and execute the addition/subtraction program.

- 5. Write a program to add the 7-byte data in memory addresses FA00H FA06H to the 7-byte data in memory addresses F900H F906H and then subtract the 7-byte data in memory addresses F940H F946H from the sum. The final result must be stored in memory with the starting address F900H.

#### Experiment 3-1:

The carry/borrow flag is used to indicate whether a carry/borrow is generated during an arithmetic or logical operation. If a carry/borrow is generated, then the flag is set to 1. Otherwise, the flag is zero. The carry flag is represented by bit Ø of the flag register.

| REG.F |  |  |  |   |              |

|-------|--|--|--|---|--------------|

|       |  |  |  |   |              |

|       |  |  |  | ~ | Carry/Borrow |

In other words, the contents of the F register will be an even number if a carry/borrow is generated during the arithmetic or logical operation. If register F is an odd number, then no carry/borrow has been generated. Load the following program into MPF-IP. Execute every instruction by using the Single Instruction method. Observe the variations of register F and record the results in the table.

| Address                                                                                                  | Machine<br>Language                                                                      | e                                                     | Assembly<br>Language                                                                                                               |                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBØØH<br>FBØ3H<br>FBØ3H<br>FBØ5H<br>FBØ7H<br>FBØBH<br>FBØDH<br>FBØDH<br>FBØEH<br>FBJØH<br>FBJØH<br>FBJØH | AF<br>3E7F<br>C6AD<br>C623<br>D613<br>D6B3<br>D615<br>AF<br>3E7F<br>CEAD<br>CE23<br>DE13 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | Language  XOR A  LD A,7FH  ADD 7,ADH  ADD A,23H  SUB A,13H  SUB A,15H  XUB A,15H  XOR A  LD A,7FH  ADC A,ADH  ADC A,23H  SBC A,13H | A,CY < Ø A < 7FH CY,A < A + ADH CY,A < A - 13H CY,A < A - 13H CY,A < A - 15H A,CY < Ø A < 7FH CY,A < A + A DH + CY CY,A < A + 23H + CY CY,A < A - 13H - CY |

| FB16H<br>FBFBH<br>FB1AH                                                                                  | DEB3<br>DE15<br>76                                                                       | 13<br>14<br>15                                        | SBC A,B3H<br>SBC A,15H<br>HALT                                                                                                     | CY,A < A - B3H - CY<br>CY,A < A - 15H - CY                                                                                                                 |

| INSTRUCTION      | (3)      | (4)      | (5)      | (6)      | (7)    |

|------------------|----------|----------|----------|----------|--------|

| BEFORE EXECUTION | A<br>7 F | <u> </u> | <u>A</u> | <u>^</u> | $\Box$ |

| AFTER EXECUTION  | + A D    | + 2 3    | - 1 3    | - B 3    | - 1 5  |

|                  |          |          |          |          |        |

|                  | CY A     | CY A     | CY A     | CY A     | CY A   |

|                  |          |          |          |          |        |

|                  |          |          |          |          |        |

|                  | (10)     | (11)     | (12)     | (13)     | (14)   |

|                  | CY       | CY       | A        | A        | A      |

|                  |          |          |          |          |        |

|                  | <u>А</u> | <u> </u> | - 1 3    | - B 3    | - 1 5  |

|                  | + A D    | + 2 3    | - CY     | - CY     | - □су  |

CY A

CY A

CY A

CY A

CY A

#### Experiment 3-2:

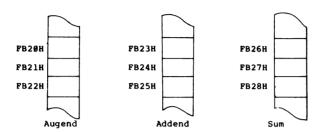

Referring to the operation for of 3-byte addition in example 3-2, write a basic addition program using only three kinds of instructions: XOR A, LD A,(nn) and ADD A,(nn). Assume that the memory addresses of the addend, augend and sum are assigned as follows:

Explanation: In the above example, we see the following rules of addition:

- (1) The addition operation moves from the low-order byte to the high-order byte, the carry generated in the low-order byte addition is added to the next higher order byte.

- (2) The addition operation is executed with the aid of the accumulator. Its result is also stored in the accumulator. Thus to add two bytes together, one byte must be loaded into the accumulator first (using the LD A, (nn<sub>1</sub>) instruction). The other byte is then added to the accumulator (using the ADD A, (nn<sub>2</sub>) instruction or the ADC A, (nn<sub>2</sub>) instruction). The final result is stored in an assigned memory address (using the LD(nn<sub>3</sub>), A instruction).

# Experiment 4 Branch Instructions and Program Loops

#### Purposes:

- To familiarize the reader with the applications of conditional and unconditional branch instructions.

- To familiarize the reader with the technique of designing program loops.

- 3. To practise using status flags in decision-making.

#### Time Required: 4 hours

- I. Theoretical Background:

- 1. Program Counter:

The program counter (PC) is an important 16-bit register in the CPU. When the voltage level of the RESET pin (pin 26) of the CPU drops to 0 and then rises to 1 (by pressing the RS key), the PC will be cleared to 0000H. The program execution is then started from address 0000H according to the clock pulses supplied by the system hardware. Once the CPU has fetched one byte of each instruction from memory, the PC will be incremented by one automatically. (The internal control circuit in the CPU determines how many bytes are contained in the instruction after the CPU has fetched the first byte of the instruction. The instruction will be executed only when the PC has been incremented by the number of bytes in the instruction). Usually, the program is fetched from the memory instruction by the instruction for execution, starting from the low memory address.

#### 2. Branch Instructions:

At any address, the PC can be changed to another address if the programmer doesn't want the program executio to continue sequentially (For instance, when there is no memory beyond that address or the program is not stored in that area). The program then jumps to another address and continue its execution. For example, the following assembly language means that the PC will be changed to 1828H after this instruction has been executed, and the program execution continues from address 1828H.

LD PC, 1828H (This instruction is illegal in Z80 assembly language.)

Actually, in assembly language, JP (Jump) is used to indicate the change in sequence of program execution. The instruction has the same meaning as LD PC, F028H

JP FØ28H

#### 3. Conditional Branch Instructions:

A conditional branch instruction performs the jump operation if some specified conditions are met. These conditions are all dependent on the data in the flag register. This function makes the microcomputer capable of responding to various external conditions. It is also an indispensable tool for designing program loops. The actions of the following instructions are described in the comments to the right of the instruction:

- CP 10H; Compare the accumulator with 10H and set the proper flag.

- ADD A,B ; Otherwise, i.e. A > 10, continue the program execution.

The condition of a conditional branch instruction is written after JP:

- (1) JP C, XXXX ; If there is a carry, or carry flag = 1, then jump to XXXX.

- (2) JP NC, XXXX ; If there is no carry, or carry flag = 0 then jump to XXXX.

- (3) JP Z, XXXX ; If zero flag = 1, or the result of previous operation is zero, then jump to XXXX.

- (4) JP NZ, XXXX ; If zero flag = 0, then jump to XXXX.

- (5) Jp PE, XXXX ; If parity flag = 1 (even parity), or there and an overflow in the previous arithmetic operation, then jump to XXXX.

- (6) JP PO, XXXX ; If P/V flag = Ø (odd parity or no overflow) then jump to XXXX.

- (7) JP P, XXXX ; If sign flag = 0 (the sign of result of previous operation is positive) then jump to XXXX.

- (8) JP M, XXXX ; If sign flag = 1 (negative) then jump to XXXX.

#### 4. Jump Relative:

To reduce the memory space occupied by the program and also reduce the cost of the microcomputer system, the Z80 microcomputer can use relative addresses to specify the displacement of a program jump. Since most displacements in a jump are within the rage between +127 and -128, a one byte number can be used to indicate this displacement. One byte of memory is saved for each jump operation compared with the two-byte absolute address in JP instructions. The operations of the following instructions are described in the commands to the right of the instruction.

- JR 10H ; Jump forward 10H (16) locations from the present program counter (the address of the next instruction). Actually, the address of the next instruction to be executed is obtained by adding 10H to the present PC.

- JR C,FOH ; If carrry flag = 1, then jump backward 10H (16) locations from the present program counter. Since the leftmost bit of FOH is 1, it is recognized as a negative number (its 2's complement is 10H).

- JR NC,7FH ; If carry flag = 0, than jump forward 127

locations (maximum value)

- JR Z,80H ; If zero flag = 1, i.e. the result of the previous operation is zero, then jump backward 128 locations. 80H (-128) is the minimum negative number that can be used in a relative address.

From the above examples, we can see that a positive relative address means jumping forward. The largest displacement then is 7FH (+127). A negative relative address means jumping backward. Its largest displacement is 80H (+128). The displacement is always measured from the address of the next instruction's op code. Relative jumps can be unconditional or conditional. The conditional jump depends on the status of the carry or zero flag. In the Z80 system, the data in the sign or P/V flag cannot be used as the condition of a relative jump.

#### 5. Program Loop:

One of the important advantages of a computer is that it can repeat the steps in a repetitive task as many times as is necessary to complete the task. This is accomplished by using a program loop. Looping is a very powerful tool in program design. A basic program loop must contain the following:

- A loopss counter preset with the number of loops to be executed. Usually, a CPU register is used as a loop counter. Of course, memory can also be used as a counter.

- (2) The loop counter is decremented by 1 after one cycle of the loop has been executed. After each cycle the value of the loop counter must be checked. If the counter is not 0, then the loop repeats until the loop counter equals to 0.

The following program can be used to add the 8-bit data in memory addresses 1900H - 190FH and store the result in the DE register pair. This is a typical application of a program loop.

| 1 6 | gister parr. in. | 15 | is a cypical application of a program loop.                                                                                                                                   |

|-----|------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | LD C,10H         | ;  | Use register C as the loop counter. Since sixteen bytes data are to be added together, 10H is preset in C.                                                                    |

|     | XOR A            | ;  | Clear the accumulator                                                                                                                                                         |

|     | LD HL,1900H      | ;  | Use the HL register pair as the address pointer The contents of the memory pointed to by HL will be added to register A. The first address is 1900H.                          |

|     | LD D,A           | ;  | Register D is used to store the carry generated during the addition operation. Clear Register D.                                                                              |

| хх  | ADD A,(HL)       | ;  | Add the contents of the memory address pointed to by HL to Register A. This instruction will be repeated 16 times. XX is assigned as the label of this instruction's address. |

|     | INC HL           | ;  | Increment HL by 1. The new HL points to the next byte in data memory to be added to Register A.                                                                               |

|     | JR NC,YY         | ;  | If no carry is generated, jump to address<br>YY to continue program execution.                                                                                                |

|     | INC D            | ;  | If a carry is generated, add this carry to Register D.                                                                                                                        |

|     |                  |    |                                                                                                                                                                               |

| YY | DEC C    | ; | Decrement register C by 1.                                                                                                  |

|----|----------|---|-----------------------------------------------------------------------------------------------------------------------------|

|    | JR NZ,XX | ; | If the result is not zero (zero flag = 0), the program loop has not finished. Jump to XX to repeat the loop.                |

|    | LD E,A   | ; | If zero flag = 1, then all data have been added together. Load A into E, the answer will be stored in the DE register pair. |

END

There are various methods of designing a program loop. Try to design the program loops described in the following illustrations.

#### II. Example Experiments:

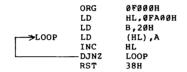

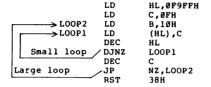

1. A program loop with a loop number of less than 256 : If the loop number is less than 256, register B is recommended as the loop counter. At the end of the loop, the DJNZ instruction can be used to decrement register B. If the result is not zero, jump to the assigned location using the relative jump method to continue the program execution. Try to analyze the following program and verify its function by loading it into the MPF-IP and executing it.

#### Experimental result:

- (1) Preset register A to  $\emptyset$  and then execute the above program Results: Contents of memory addresses F900H - F91FH:

- (2) Preset register A to 55H and execute the above program. Results:

Contents of memory address F920H:

(3) Preset register A to 64H and replace the second instruction LD B,20H by the instruction LD B,0 . Execute the program again. Results:

Contents of memory addresses F900H - F9FFH:

#### 2. Nested loops:

In a more complicated program, a loop can be totally nested or embedded inside another loop. The following program can be used to divide the 256 bytes of data stored in memory into 19 groups. The starting address of the memory is F900H. Put the contents of each group of data in the form of a hexadecimal number:

0.....(lst set), l.....(2nd set), 2.....(3rd set),.....F.....

(19th set).

- Translate the above program into machine language and then load it into the MPF-IP. Execute the program. Results:

- (2) Revise the above program such that the 19 bytes of the first group are all "F", and the 16 bytes of the last group are all "0".

- 3. A program loop with loop number larger than 256: If the loop number is larger than 256, a 19-bit register can be used as the loop counter. But, in the Z80 system, incrementing or decrementing a 16-bit register can not affect the status flag. Thus, some auxiliary instruction is used to determine whether the loop counter is zero. The following program is supposed to be able to set all data in RAM F980H FAFFH to AAH. Try to find the errors in this program and correct them. Load the correct program into the MPF-IP and record the result of the program execution.

ORG ØFØØØH BC,0180H L.D HL.ØF98ØH LD LD (HL), ØAAH T.OOP INC HL DEC BC NZ,LOOP JR HALT

- 4. A program 'loop without a down counter: A program loop need not use a down counter. The function of the down counter can be replaced by using an up counter or using the method of address comparision or data comparison. Study the method used in the following program loops. Load the programs into MPF-IP and execute them.

- (1) Move the data string in the memory (RAM) section with starting address FAØØH to the memory (RAM) section with starting address F9ØØH. The movement will be terminated when data @FFH is found.

|      | ORG | ø F Ø Ø Ø H |

|------|-----|-------------|

|      | LD  | HL,ØFAØØH   |

|      | LD  | DE,ØF9ØØH   |

| LOOP | ĿÐ  | A,(HL)      |

|      | LD  | (DE),A      |

|      | CP  | ØFFH        |

|      | JR  | Z,EXIT      |

|      | INC | HL          |

|      | INC | DE          |

|      | JR  | LOOP        |

| EXIT | RST | 38H         |

(2) Replace all the data stored in the memory section starting from the address pointed to by HL to the address pointed to by DE by their corresponding 2's complement. In testing the program, the values of HL and DE must be preset first. The value of HL must be larger than that of DE.

|      | ORG | ØFØØØH  |

|------|-----|---------|

| LOOP | LD  | A, (HL) |

|      | NEG |         |

|      | LD  | (HL),A  |

|      | INC | HL      |

|      | AND | Α       |

|      | SBC | HL,DE   |

|      | ADD | HL, DE  |

|      | JR  | NZ,LOOP |

### Experiment 5 Stack and Subroutines

#### Purposes:

- 1. To understand the meaning and applications of the stack.

- 2. To understand the designing techniques and applications of subroutines.

#### Time Required: 4 hours

- I. Theoretical Background

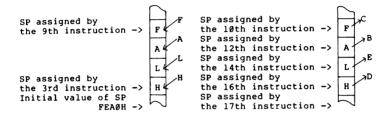

- 1. Stack: In program design, a stack is recognized as a memory section which has only one port for input and output. Data are written in or retreived from stack via this port. The first data placed in stack is said to be at the bottom of stack. The data most recently placed in stack is said to be at the top of stack. Thus, a stack is also called a last-in first-out memory. A stack can be constructed by hardware shift registers or general RAMs. In the 280 microcomputer system, the programmer can assign a region of RAM as the stack. To define a stack at the top of RAM, the highest address of RAM is incremented by 1 and then loaded into the stack pointer (SP) in the CPU. The following program and diagrams illustrate the operation of stack.

### Instruction Instruction

#### Comment

- (1) LD SP, OFEACH

- (2) DEC SP

- (3) LD (SP),H

- (4) DEC SP

- (5) LD (SP), L

- (6) DEC SP

- (7) LD (SP),A

- (8) DEC SP

- (9) LD (SP), F

- ; Stack pointer is set to OFEAOH, i.e. the RAM section with address less than or equal to FEAOH is assigned as stack.

- ; Decrement SP by 1. Stack pointer is at FE9FH, i.e. at the bottom of stack.

- ; Load the contents of register H into memory (RAM) address FE9FH.

- ; Decrement SP by 1 again.

- ; Place the contents of L at the top of stack (i.e. above H).

- ; Place the contents of A at the top of stack (i.e. above L).

- ; Place the contents of F at the top of stack (i.e. above A).

•

| (10)                 | LD C, (SP)                 | ; Pop one byte of data from the top<br>of stack and move it to register C.                                                          |

|----------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| (11)                 | INC SP                     | ; Increment SP by 1. SP is moved towards the top of the stack.                                                                      |

| (12)<br>(13)<br>(14) | LD B,(SP) INC SP LD E,(SP) | <pre>, Pop data from the top of stack. ; Increment SP by 1 again. ; Pop data from the top of stack and move it to register E.</pre> |

| (15)<br>(16)         | INC SP<br>LD D,(SP)        | ; Pop data from the top of stack and<br>move it to register D. This data is the<br>first one that is stored in stack.               |

| (17)                 | INC SP                     | ; SP is at the initial value.                                                                                                       |

RAM RAM

Push data onto the stack

Pop data from the stack

From the above illustrations of stack operation, we can see that data can be stored in RAM by using SP as the pointer. SP is decremented by 1 whenever one-byte of data is stored in and the stack area becomes larger. The SP will be incremented by 1 whenever one-byte data is retrieved from the stack area and the stack area becomes smaller. The process of decrementing SP (pushing data onto stack) or incrementing SP (popping data out of stack) can be accomplished automatically by special hardware design. A stack can also be used to store a 16-bit address (or data). In the Z80/8085 system, there are instructions to push a 16-bit register pair onto stack and pop a 16-bit data out of stack. During each operation, SP is decremented or incremented by 2. The following program is equivalent in function to that of the program given above.

```

LD SP, 0FEA0H ; Same as 1st instruction.

PUSH HL ; Same as no. (2)(3)(4)(5) instructions.

PUSH AF ; Same as no. (6)(7)(8)(9) instructions.

POP BC ; Same as no. (10)(11)(12)(13) instructions.

POP DE ; Same as no. (14)(15)(16)(17) instructions.

```

Instructions PUSH and POP can be used to temporally store data in registers and also used to transfer register data. An example is given below.

```

PUSH BC

POP IX ; Move the 16-bit data in BC to IX

PUSH HL

AND A

SBC HL,DE ; Compare HL with DE to generate status ; flags. The value of HL is kept ; unchanged.

POP HL

```

It is a very important that the number of PUSH instructions be equal to the number of POP instructions in the stack operation.

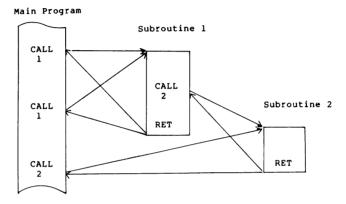

#### 2. Subroutine:

Programs for arithmetic (addition, subtraction, multiplication or division), keyboard and display control, etc are often used as part of a large program in practical applications. If the programmer rewrites these small programs everytime he needs them, the whole program would be very tedious to write. To save memory space for the program and reduce errors, subroutines are often used in a large program. Instructions CALL and RET are used to manipulate the subroutines. The subroutines can be executed unconditionally or according to the conditions of flags. The instruction CALL in the main program is used to call the subroutine. Its function consists of two operations which are illustrated below.

```

CALL @FA38H ; Call the subroutine stored in address @FA38H.

Equivalent to

PUSH PC ; Push the current program counter onto stack.

JP @FA38H ; Jump to address FA38H and continue the program execution.

```

RET instruction does'nt need an operand (1 byte instruction), it is the same as 'POP PC' instruction.

```

RET ; Return to original program and continue to execute.

Equivalent to ; Retrieve 16-bit data instack and load into PC, then ececute program according PC; contents.

```

Calling a subroutine is an important step in a program. Subroutines in a program can be in a nested form that is a subroutine can be another subroutine. The relationship is shown below:

Usually, subroutines are written by a specialist. The user only has to understand its calling rocedure. If the subroutine is written by the user himself, the following items must be considered in the design:

- (1) An easily-remembered name must be chosen for the subroutine.

- (2) How to get the data required in the subroutine before executing the subroutine.

- (3) How to express the result after executing the subroutine.

- (4) Which register will be changed after executing the subroutine.

- (5) How much memory will be occupied by the subroutine and how much time is needed for the CPU to execute the subroutine.

The following must also be considered when a subroutine is called by the main program:

- (1) Registers that should not be changed by the execution of the subroutine must be pushed onto stack before calling the subroutine.

- (2) How the results obtained from the subroutine execution will be transmitted by the main routine (the calling routine).

The following listing is a sample subroutine named MADD. It can be used for multi-byte BCD addition.

```

MADD

LISTING

PAGE 1

LOC

OBJ CODE

STMT SOURCE STATEMENT

ASM 3.0

1 ; *** MULTIBYTE BCD ADDITION ROUTINE ***

2 ; ENTRY: HL POINTS TI LOW ORDER BYTE OF AUGEND

3 ;

DE POINTS TO LOW ORDER BYTE OF ADDEND

4 ;

B = BYTE NUMBER, 1 BYTE = 2 BCD DIGIT

5 ; EXIT : IX POINTS TO LOW ORDER BYTE OF RESULT

6 ; REG. CHANGE : AF,B,HL,DE,IX

7 : MEMORY USED : 15 BYTES

R

FRAA

AF

9 MADD

XOR A ; CLEAR CARRY FLAG

FBØ1

1A

10 MADD1

LD A, (DE)

FBØ2

86

11

ADD A, (HL)

FBØ3

27

12

DAA

FRØ4

DD7700

13

LD (IX),A

FBØ7

13

14

INC DE

15

FBØ8

23

INC HL

FBØ9

DD23

16

INC TX

DJNZ MADD1

FRØR

10F4

17

FBØD

C9

18

RET

```

Two 4-byte BCD data are stored in the memory with starting addresses at  $\theta F A \theta \theta H$  and  $\theta F A \theta \theta H$ , respectively. To add the BCD data together and store the result in RAM address FA  $\theta H$ , subroutine MADD is called by the following procedure:

```

LD B, 4 ; Set Byte Number = 4 .

LD HL, ØFAØØH ; Hl points to the address of augend.

LD DE, ØFAØØH ; DE points to the address of addend.

LD IX, ØFAØØH ; IX points to the address of sum.

CALL MADD

```

#### II. Example Experiment:

- (1) Using the instructions for stack operation, write a routine to move the data in HL, DE and BC to HL', BC' and DE', respectively. Load the program into MPF-IP and execute it.

- (2) In the following program, a small loop is embedded in a large loop. The function of this program is to shift all the 8-bit the data in bytes in the address FAllH - FA20H left four bits. Use register B as the loop counter for both small and large loops. Load the program into MPF-IP and execute it. Discuss the reason why register B can be used as the counter for both loops.

| F800 |        | 1  |       | ORG ØF8ØØH    |

|------|--------|----|-------|---------------|

| F800 | 0621   | 2  |       | LD B,21H      |

| F8Ø2 | 21001A | 3  |       | LD HL, ØFA4ØH |

| F8Ø5 | C5     | 4  | LOOP1 | PUSH BC       |

| F8Ø6 | 7E     | 5  |       | LD A, (HL)    |

| F8Ø7 | 0604   | 6  |       | LD B,4        |

| F8Ø9 | 87     | 7  | LOOP2 | ADD A,A       |

| F8ØA | 10FD   | 8  |       | DJNZ LOOP2    |

| F8ØC | 77     | 9  |       | LD (HL),A     |

| F8ØD | 23     | 10 |       | INC HL        |

| F8ØE | Cl     | 11 |       | POP BC        |

| F8ØF | 10F4   | 12 |       | DJNZ LOOP1    |

| F811 | 76     | 13 |       | HALT          |

- (3) By calling the subroutine given in part I (multi-byte BCD addition routine), write a program to add two 8-byte data stored in memory FA00H and FA08H. The result must be stored in the 8-byte memory starting at 0FA40H.

- (4) Revise the above program for BCD subtraction or multi-byte binary addition/subtraction. Test the program and record the method of revision used.

- (5) Write a subroutine to change the 16-bit data in HL to its 2's complement. Write a main program to change the data in IX and IY to their 2's complements. Load the program into MPF-IP and test it.

- (6) By using the above routine for complementing the HL register pair, write a program to subtract DE from the data in IY and store the result in IY.

# Experiment 6 Rotate, Shift Instructions, and Multiplication Routines

#### Purposes:

- 1. To understand the use of Rotate and Shift instructions

- To understand the designing techniques and uses of a binary multiplication subroutine.

#### Time Required: 4 - 8 hours

#### I. Theoretical Background:

- 1. The 9-bit data formed by the carry flag and 8-bit data in a register or memory can be shifted one bit left or right by ROTATE or SHIFT instructions. The ROTATE and SHIFT instructions are mainly used for multiplication and division. We multiply a number by rotating and shifting left the bits that constitute a number, while a division operation is done by rotating or shifting right the bits that constitute a number. There are many ways to rotate or shift the bits of a number. So, there are 13 different types of ROTATE and SHIFT instructions. Please refer to the MPF-IP User's Manual, Appendix C. The mnemonic codes of these instructions are described below.

- (1) If the leftmost character of an instruction is "R", it is a "ROTATE" instruction. Such instructions can be used to rotate the 9-bit data (formed by 8-bit data and carry flag) left or right one bit, e.g. RLCA, RL, RRA, etc.

If the leftmost character is "S", then it is a "SHIFT" instruction. All the 9-bits of the data are shifted left or right by one bit. The bit shifted out from one side will not be moved in from other side. Examples of such instructions are SAL and SRL.

- (2) If the second character from the left is "R", it means "shift right" or "rotate right". Instructions RR, SRL, RRCA, etc. are examples. If the second character in the left is "L", it means "shift left" or "rotate left". Instructions RL, SLA, RLCA, etc. are the examples.

- (3) The meaning of the third character is more complicated, but it can be summarized as follows:

- (a) In ROTATE instructions:

The third character "C" represents the circular rotation of 8-bit data, carry flag is not included. The third character (or the fourth character) "A" means that this instruction is operated with the accumulator.

Instructions RLA, RRA, RLCA and RRCA are examples.

The third character "D" indicates the shift operation on decimal or hexadecimal numbers, for example, RLD and RRD. These instructions are designed to rotate the memory pointed to by HL left or right one digit (4 bits) The digit entering from the left or right direction comes from bit 0 bit 3 of the accumulator. The digit moving out from the other side is sent to bit 0 bit 3 of the accumulator.

- (b) In SHIFT instructions:

The third character "A" indicates "Arithmetic Shift".

Binary data shifted left means multiplying it by 2.

Binary data shifted right means dividing it by 2. Two

of these instructions are SLA and SRA. Because bit 7 is

assigned as "sign bit" and the sign of the data is not

changed by these operations, the leftmost bit (bit 7)

must be kept unchanged.

The third character "L" means "logical shift".

Instruction SRL is an example. In these operations, a

"0" is always moved to bit 7 from the left direction.

#### 2. Binary Multiplication:

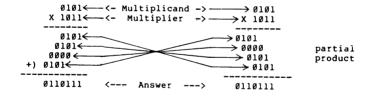

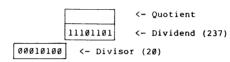

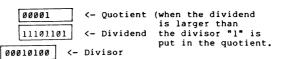

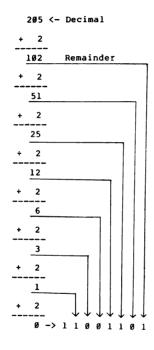

The operation of unsigned binary multiplication can be accomplished by shifting the binary number left or by a program loop of addition. An example of binary multiplication by hand-calculation is illustrated below.

In the above calculation, one bit of the multiplier is checked. If that bit is 1, the multiplicand is copied as the partial product. If that bit is 0, 0000 is given instead. The position of the partial product is arranged such that the least significant bit of the multiplicand is aligned with the bit of the multiplier being checked. In this example, multiplicand and multiplier are both 4-bit data. Thus, it is necessary to repeat the operations of checking, shifting and addition four times. Similarly, the operations must be repeated 8 times for 8-bit data multiplication and 16 times for 16-bit data multiplication. In the left-hand side calculation given above, the bit-checking process starts from the least significant bit of the multiplier. In the right-hand side calculation, the bit-checking process starts from the most significant bit. But the results of the two calculations are identical. The program of binary multiplication for microcomputers can be designed by a method similar to the above calculation.

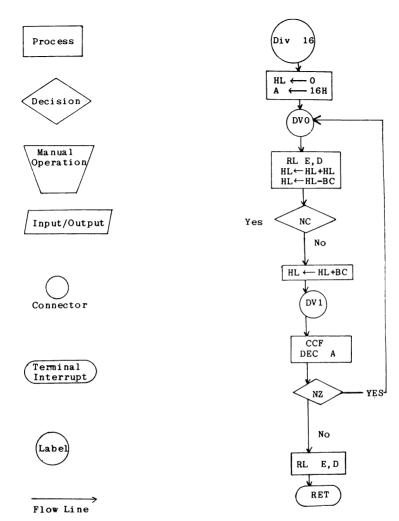

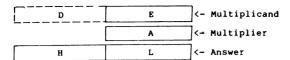

Example: Multiply the 8-bit data in register E by the 8-bit data in register A. The product is stored in the HL register pair.

Answer: Specific registers have been assigned to store multiplicand, multiplier and product according to the characteristics of the Z80 instruction set. Using the calculation algorithm given in the right-hand side of the above example, the program is designed as follows.

- 1. In the above hand calculation, the bit-checking process starts from the least significant bit. A program loop can be employed in the example. The multiplier is 8-bits long, thus the loop number is equal to 8. In every loop execution, the bit being checked (in register A) can be shifted into the carry flag by the RLCA instruction. Then, according to the condition of the carry flag, we can decide what will (or will not) be done next.

- 2. If the first bit checked (the leftmost bit) is 1, the partial result is actually obtained by shifting the multiplicand left (n-1) bits, where n is the number of bits in the multiplier. The other partial results are obtained by shifting the partial products left (n-2) bits, (n-3) bits,...., etc. In this example, no other registers are required to store the partial results. Each partial result can be added directly to the HL register pair.

- 3. From the above description, we can see that the partial products must be shifted left (n-1) bits, (n-2) bits, (n-3) bits,...,etc. Since the bit-checking is also moving left in the process, we can generate a new intermediate result by immediately adding each partial product to the previous intermediate result. This method is more efficent and is used in the following program flowchart.

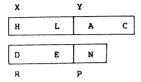

#### 4. Register Assignments:

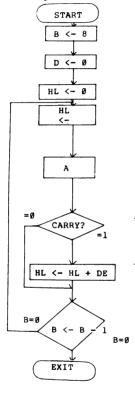

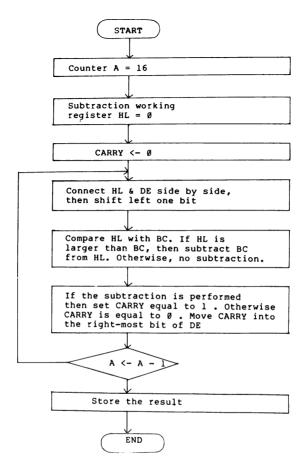

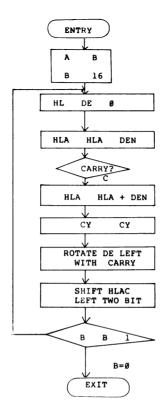

#### 5. Program Flowchart :

- <- Set B as the loop counter. For an 8-bit multiplier, B is set to 8

- <- 16-bit addition will be performed. First clear D.

- <- Set the initial value of answer to 0 .

- <- Shift the intermediate result left one bit. The first shift process is invalid. Thus the first partial product will be shifted left n-l bits after the loop is executed once.

- <- The leftmost bit of the multiplier is moved to the carry flag for testing.

If the leftmost bit of the multiplier is 1, the multiplicand is added to the intermediate result.

Otherwise, the addition is ignored.

<- Check if the program loop has been completed. If it is, stop execution. Otherwise, repeat the loop operation.

#### MP8 LISTING

### LOC OBJCODE STMT SOURCE STATEMENT ASM 3.0

1;\*\*\*MULTIPLY\*\*\*

2:ENTRY:

3 ;MULTIPLER IN E

4 ; MULTIPLICAND IN A

5; EXIT:

6 ; PRODUCT IN HL

7; REG CHANGE : B,D,HL

8; MEMORY BYTE : 14

9; EXECUTION TIME :<395 CLOCK / 221.2 us.

10;

11MP8:

| FB00 | 0608       | 12MULTI | LD B,8      | ;SET BYTE COUNTER=8       |

|------|------------|---------|-------------|---------------------------|

| FBØ2 | 1600       | 13      | LD D,Ø      |                           |

| FBØ4 | 62         | 14      | LD H,D      |                           |

| FBØ5 | 6 <b>A</b> | 15      | LD L,D      | ;CLEAR D,HL REGISTER      |

| FBØ6 | 29         | 16 LOOP | ADD HL, HL  | ;SHIFT HL LEFT            |

| FBØ7 | <b>Ø</b> 7 | 17      | RLCA        | ;ROTATE BIT 7 OF "A" INTO |

|      |            |         |             | ;CARRY FLAG               |