# Assembly Language Programming on the Sinclair QL

Programming the 68008 microprocessor

**Andrew Pennell**

# Assembly Language Programming on the Sinclair QL

Programming the 68008 microprocessor

**Andrew Pennell**

First published 1984 by: Sunshine Books (an imprint of Scot Press Ltd.) 12–13 Little Newport Street London WC2R 3LD

# Copyright © Andrew Pennell, 1984

- © The contents of the QL are the copyright of Sinclair Research Ltd.

- ⊕ Quill, Archive, Abacus and Easel are Trade Marks of Psion Software Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means; electronic, mechanical, photocopying, recording and/or otherwise, without the prior written permission of the Publishers.

British Library Cataloguing in Publication Data Pennell, Andrew

Assembly language programming on the Sinclair QL.

- 1. Sinclair QL (Computer)—Programming

- 2. Assembler language (Computer program language)

- I. Title

001.64'24 OA76.8.S625

ISBN 0-946408-42-4

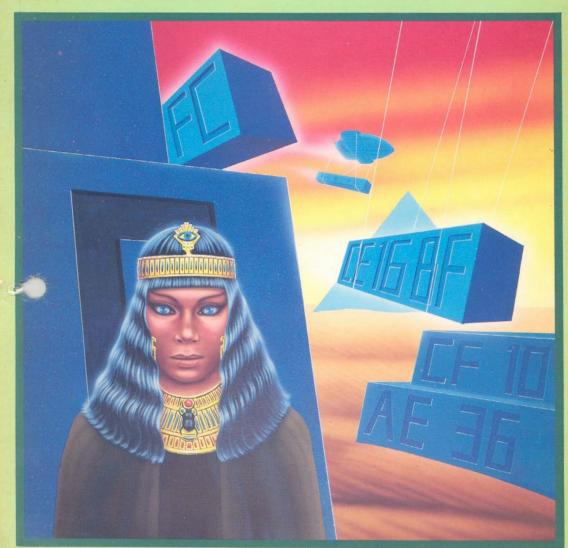

Cover design by Grad Graphic Design Ltd. Illustration by Stuart Hughes. Typeset by Paragon Photoset, Aylesbury. Printed in England by Short Run Press Ltd, Exeter.

# **CONTENTS**

| Introduction                         |                                             |     |  |  |

|--------------------------------------|---------------------------------------------|-----|--|--|

| 1                                    | Memory, Bits and Bytes                      | 1   |  |  |

| 2                                    | Inside the QL                               | 7   |  |  |

| 3                                    | The MOVE Instruction and Addressing Modes   | 13  |  |  |

| 4                                    | Condition Codes, Branching and Arithmetic   | 25  |  |  |

| 5                                    | Further Instructions and Passing Parameters | 41  |  |  |

| 6                                    | Exception Processing, Traps and Interrupts  | 47  |  |  |

| 7                                    | Using the Hardware and Firmware             | 57  |  |  |

| 8                                    | An A–Z of the 68008 Instruction Set         | 69  |  |  |

| 9                                    | The 68008 Disassembler                      | 133 |  |  |

| 10                                   | Other 68000 Series Devices                  | 155 |  |  |

| Epilogue: Multi-tasking — an Example |                                             |     |  |  |

| References                           |                                             | 165 |  |  |

| Index                                |                                             |     |  |  |

# Contents in detail

#### CHAPTER 1

#### Memory, Bits and Bytes

Memory — ROM — RAM — hex — binary — two's-complementing — SuperBASIC functions.

#### **CHAPTER 2**

#### Inside the OL

What makes the QL tick — 68008 registers — status register — supervisor and user modes — memory map — storing machine code — hex loader.

#### **CHAPTER 3**

# The MOVE Instruction and Addressing Modes

The MOVE instruction — addressing modes — stack pointer — other MOVEs.

#### **CHAPTER 4**

# Condition Codes, Branching and Arithmetic

Condition codes — SUB instruction — branches — CMP instruction — looping using DBcc — subroutines — CLR instruction — ADD — OR — EOR — shifts and rotates — printing in hex.

#### **CHAPTER 5**

# Further Instructions and Passing Parameters

LEA—NOP—EXG—NOT—NEG—SWAP—passing parameters.

#### **CHAPTER 6**

# **Exception Processing, Traps and Interrupts**

Exception processing — vector table — interrupts — traps — user-defined exceptions.

#### CHAPTER 7

# Using the Hardware and Firmware

The screen — colour modes — plotting points — printing characters — the 8049 — scanning the keyboard — the alternate screen — disabling QDOS.

#### CHAPTER 8

# An A-Z of the 68008 Instruction Set

Calculating addressing bytes — addressing modes — complete instruction set.

#### **CHAPTER 9**

#### The 68008 Disassembler

The algorithm — disassembler — description — converting to machine code — full version.

#### CHAPTER 10

# Other 68000 Series Devices

Other 68000 series processors — support devices — the 68881 maths processor — 68486/7 graphics system.

# Introduction

The Sinclair QL has been hailed as a major breakthrough in personal computing and in part this is because of the microprocessor it uses — the Motorola 68008. Since its launch the machine has been the subject of much controversy particularly when delivery dates were not fulfilled. Even before its production problems were known there was comment on the claims made by the advertisements saying that the QL was a '32 bit' machine. Critics argued that it was only an 8 bit machine.

This book is concerned with the 68008 and programming it on the QL. I would hope that by the end of this book you will be able to form your own conclusions as to whether it is a 32 bit device or not. I personally feel that it has the power of a 32 bit chip, but not the speed.

If you have programmed any 8 bit devices before, you will probably find programming the 68008 easy, compared with whatever you've used previously. On the other hand, if this is your first processor, you will think all the 8 bit chips are positively prehistoric in comparison, and you could well be right!

#### Credit where it's due

I would like to express my sincere thanks to the following:

My parents and friends, for their patience while I wrote this; Mike Salem and David Link for their invaluable technical assistance; Sinclair Research for inventing the QL and supplying technical information; Motorola for inventing the 68000 series and supplying data on it; All those at Sunshine for persuading (and bullying) me to get this done; and Apple, for teaching Macintosh about Man.

Andrew Pennell Cliftonville, Kent August 1984

# CHAPTER 1

# Memory, Bits and Bytes

This chapter aims to introduce all the technical terms used in the rest of the book, and is intended for the newcomer to machine-code programming. However, even if you've done machine code on other machines, you should still find some of this is new to you.

The two most important parts inside any computer are its memory, and its processor. The memory stores all the programs and data, which is required for the processor to work properly. Within the memory, everything is stored as numbers, even if it seems as if it is storing words, like LET and PRINT. What the numbers actually mean and do depends on how they are used. Memory is referred to by its *address*. A memory address is a number from 0 up to, well, it depends, normally on the QL it stops at 262143. At each address, *data* is stored, in the form of a number from 0 to 255, which is known as a *byte*. All memory can have its contents inspected, by *reading*, and in SuperBASIC the function PEEK is the way to read memory. For example, to see what numbers lie from address 0 up to address 40, a BASIC program like this could be used:

- 10 FOR i = 0 TO 40

- 20 PRINT "At address ";i;"the data is";PEEK(i)

- 30 NEXT i

11

which will produce various numbers, and you will notice that all the data lies between 0 and 255, as it should. (Don't worry about what these particular numbers mean — they are explained later, in Chapter 7.)

There are two types of memory, RAM and ROM. ROM stands for Read Only Memory, and its contents are permanently fixed at the time of manufacture. It is used for storing things that must always be in the machine, and on the QL the ROM contains the SuperBASIC language, and the QDOS operating system.

RAM stands for Random Access Memory, and can be read, like ROM, and also written to, so its contents can be altered. Things like Super-BASIC cannot be stored in RAM because its contents are lost when the power is removed, unlike ROM. On the QL, the RAM is used for storing things that need to be changeable including the screen display and BASIC programs. To alter RAM contents from SuperBASIC, the POKE

command is used, followed by two numbers — the first is the address you want altered, and the second is the data you want to put in. POKing into ROM has no effect of course.

#### **Hex and Binary**

Most of us have ten fingers so we all count in base 10. It would be much more useful if we all had 16 fingers for computer work, as base 16, or hexadecimal as it is known, is a very common way of expressing numbers when programming in machine code. As we have only 10 digits, to denote numbers between 10 and 15, we use the first six letters of the alphabet. Thus, the number 12 decimal is C in hex. The way of denoting hex numbers varies on different machines, but on the QL the usual way is by preceding them with a dollar sign, so 12 is \$C. With numbers greater than 15, we use extra digits, like we do with numbers greater than 9 in decimal, so the number 30 is \$1E (as 30=1\*16+14), and so on, for up to eight digits. There are two reasons for using hex. The first is that it is much more concise for bigger numbers — for example, the number 524288 is rather unwieldy compared with the hex version of \$80000. The other reason is that it is easy to convert between hexadecimal and another base useful for computing — binary.

### Binary

Binary is used frequently in computing and is number base 2. Thus you can have only the digits 0 and 1 in a binary number. For a byte, which ranges from 0 to 255 decimal, the binary equivalent ranges from 0 to 11111111. Each binary digit counts a power of two, so the rightmost digit is the 1s column, the next one the 2s, the next the 4s, and so on. So, to convert the decimal 30 into binary, we need to write it as a sum of powers of two, which works out to be 16+8+4+2, giving a binary of 11110. It is usual for binary digits to be written in multiples of eight, so 30 decimal is equivalent to 00011110 binary. Each binary digit is known as a bit, and a byte has eight bits. The bits themselves are numbered, starting at 0 for the rightmost, and going up. This can be made a little clearer by a diagram:

| Bit number | 7   | 6  | 5  | 4  | 3 | 2 | 1 | 0               |

|------------|-----|----|----|----|---|---|---|-----------------|

| Power of 2 | 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1               |

| Example:   | 0   | 0  | 0  | 1  | 1 | 1 | 1 | 0 = 30  decimal |

The largest bit number is known as the *most significant bit*, which is bit 7 (byte), bit 15 (word), or bit 31 (long).

Half a byte is, believe it or not, a nibble, and has four bits. To convert between hex and binary, each nibble corresponds to a hex digit, so in the

example above the nibble 0001 corresponds to 1, and 1110 to E.

A byte is the basic unit of storage. 1024 bytes (2 ^ 10) is known as a kilobyte, denoted by K, and 1024K is known as a megabyte, or M. The 68008 uses two other units — words, and long words.

A word is two bytes, and must always start at an even numbered address. It can hold a value of between 0 and 65535, (=\$0000 to \$FFFF). The first byte in a word is known as the 'high byte', or most significant byte (MSB), and contains the leftmost hex pair of digits. The second byte is the 'lower byte', or least significant byte (LSB), and contains the rightmost pair of digits. For example, if the word data \$1234 was stored at address 30, then location 30 would hold \$12, and location 31 would hold the \$34 part of the data. (This is the opposite order to most 8 bit processors.) SuperBASIC has two commands for handling word quantities—there is

PEEK\_ W(address) which is equivalent\* to 256\*PEEK(address)+PEEK(address+1)

for reading words from memory, and there is

POKE\_W address,data which is directly equivalent to POKE address,data DIV 256: POKE address+1,data MOD 256

for writing words into memory.

A long word is four bytes (two words) and must also always be at an even numbered address. It can hold a value of between 0 and 4294967295 (=\$000000000 to \$FFFFFFFF). The first byte holds the most significant byte of the data (ie the leftmost two digits), then the next most significant byte, and so on for all four bytes. For example, if the long data \$12345678 was stored at location 30, then location 30 would hold \$12, location 31 \$34, location 32 \$56, and location 33 \$78. There are two SuperBASIC commands for handling long quantities:

PEEK\_L address which is equivalent\* to 65536\*PEEK\_W(address)+PEEK\_W(address+2)

and

POKE\_L address,data which is equivalent to POKE\_W address,data DIV 65536: POKE\_W address+2,data MOD 65536

(\*The functions are not exactly equivalent because PEEK\_W and PEEK\_L give signed results. If the value is greater than \$7FFF and \$7FFFFFFF respectively then the number is two's-complemented—see below.)

# Two's-complementing and sign extension

As we have seen, the different sizes of numbers can range from 0 to 255 (byte), 65535 (word), and 4294967295 (long). However, there is an alternative way of reading numbers, in order to get both negative and positive results.

We shall deal with byte quantities first. If a number is said to be held in 'two's-complemented' form, this means that the number can be positive or negative, depending on its highest bit — bit 7 in the case of bytes. If the bit is 0, or *reset*, then the number is as usual. However, if bit 7 is 1, or *set*, then the number is taken as negative, by subtracting 256 (in the case of bytes). Thus, numbers stored as 0 to 127 are the same if stored as two's-complemented, but numbers between 128 and 255 correspond to the values of -128 to -1 respectively (from 128-256 and 255-256). Thus in two's-complement form, a byte can have a range of -128 to 127 inclusive.

Two's-complementing with words is similar, except the bit that determines the sign is bit 15, and negative values are calculated by subtracting 65536. Thus numbers from 0 to 32767 mean just that, but numbers between 32768 and 65535 correspond to the values -32768 to -1, respectively. Thus a two's-complement word can have a value between -32768 to 32767.

With long words, the sign bit is bit 31, and negative values are calculated by subtracting 2147483648 (=\$8000000), giving a range of -\$80000000 to \$7FFFFFFF inclusive.

Sign-extension is when the most significant bit of data is transferred to all the higher bits, when changing sizes. For example, the byte \$86 would be sign-extended to a word of \$FF86, and then to a long word of \$FFFFFF86. Thus 'negative' numbers get FFs added, while positive numbers get 00s. The reason for sign-extension is to retain the same two's-complement value — \$86 (byte) is -122, and so are \$FF86 (word), and \$FFFFFFF86 (long). The PEEK\_W and PEEK\_L functions always give signed results in SuperBASIC.

# The processor

The processor in a machine is the controller of everything else. For it to work, it must have a machine-code program to execute, and programs are stored as numbers in the memory of the machine. It would be extremely

difficult to write machine code with just numbers, so designers of each processor invent a way of expressing what the processor does in combinations of words and numbers, called mnemonics. A machine-code instruction is written by us humans using mnemonics, then converted, either by hand or by another program called an *assembler*, into the numbers that the processor requires. The numbers corresponding to each instruction are known as *opcodes*. For example, the instruction

#### JMP \$1234

while it probably doesn't mean much to you at the moment, means a lot more than its opcode would, which is \$4EF81234. This book is concerned with programming the 68008 processor using mnemonics and instructions, and the actual method for converting instructions, that humans understand, into opcodes, that the processor understands, will be covered later.

When writing machine code, it's usual to denote all references to locations not by their address, such as \$1234, but by a word, known as a *label*, like PRINT. This has the advantage of being easier to understand, and easier to work out. It's also common to add text to the ends of instructions, known as comments, that describe what the instruction does. For example, a line like

LOOP JSR PRINT print the character

is a lot clearer than the functionally equivalent

JSR \$1234

In the first line both LOOP and PRINT are labels, with the comment following the first line after the instruction.

# **Useful SuperBASIC functions**

Converting between decimal and hex can be a bit tricky at times, so why not use SuperBASIC to do the conversions. Functions *hex\$* and *bhex\$* take a word or long word respectively in decimal and convert it to a four or eight digit hex string, while function *dec* does the reverse.

#### **Listing 1.1: Hex-Decimal Functions**

100 DEFine FuNction h1\$(a)

110 RETurn CHR\$(48+a+7\*(a>9))

120 END DEFine

```

130 DEFine FuNction h2*(a)

140 RETurn h1$(a DIV 16)&h1$(a MOD 16)

150 END DEFine

160 DEFine FuNction hex*(b)

170 LOCal a,h*

180 a=pos(b):IF a>32767 THEN a=a-32768

190 h==h2*(a DIV 256)&h2*(a MOD 256)

200 \text{ IF pos}(b) > 32767 \text{ THEN } h*(1) = h1*(h*(1))

+8)

210 RETurn h*

220 END DEFine

230 DEFine Function bhex*(a)

240 LOCal h1.h2

250 h1=INT(a/65536):h2=a-65536*h1

260 RETurn hex#(h1)&hex#(h2)

270 END DEFine

280 DEFine Function pos(a)

290 IF a<0 THEN RETurn 65536+a:ELSE RETu

rn a

300 END DEFine

310 DEFine FuNction dec(a*)

320 do dec(a$):RETurn dd

330 END DEFine

340 DEFine PROCedure do_dec(as)

350 LOCal s.t.o

360 t=0:o=LEN(as)

3700 \text{ s=CODE}(a\$(q))-48:IF \text{ s}>22 \text{ THEN s=s}-32

380 IF s>9 THEN s=s-7

390 t = t + s * 16^{(LEN(a*) - q)}

400 a=a-1:IF a>0 THEN GO TO 370

410 dd=t

420 RETurn

430 END DEFine

```

(These functions are not the neatest way of converting between the bases. They have been written in such a way as to work on early bug-ridden versions of the QL, as more concise versions can crash such machines.)

# **CHAPTER 2**

# **Inside the QL**

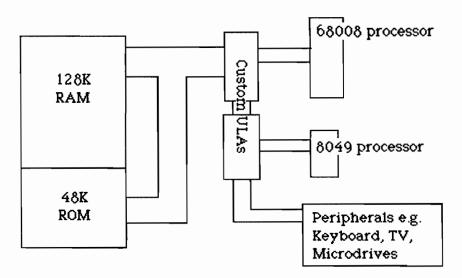

Inside your QL is a lot of the latest in electronic technology. There are many components to it, but the main ones that interest us are shown in **Figure 2.1**.

Figure 2.1: QL Main Components.

The main microprocessor is the Motorola MC68008, which works in conjunction with a slave processor, an Intel 8049. This book is mainly concerned with the former, though the use of the latter is covered in Chapter 7. The 68008 is a direct development from the MC68000, which was first introduced in 1979 in limited quantities. The -8 version is very similar to its predecessor, and is almost completely software-compatible. The main differences between them are the number of data and address lines — the 68000 has 16 data and 24 address lines, and can address 16 Mbytes, while the -8 has only 8 data and 20 address lines, and can address 1 Mbyte. The difference in data lines had the effect that the -8 runs rather slower than its counterpart. The 68008 is a very new device, first appear-

ing at the end of 1983. The Sinclair QL is the first computer to use the processor.

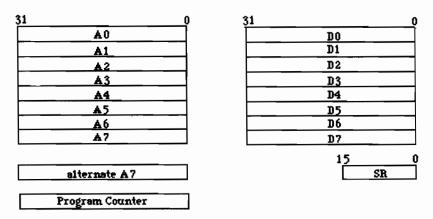

Figure 2.2: 68008 Register Set.

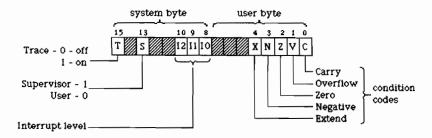

A simplified functional diagram of the 68008 is shown in Figure 2.2. Internally there are eight address registers, named from A0 to A7, a special alternate A7 register, eight data registers, named D0 to D7, program counter, and status register. All but the latter are 32 bit registers, while the status register (known as the SR) is 16 bit. Address register A7 is a special case, as it is also the stack pointer register. The 68008 can run in two different states, *supervisor* and *user* modes. Each mode requires its own stack pointer, hence the existence of two A7s. The current mode, and A7 usage, is defined by a bit in the status register. The uses of all the bits is shown in Figure 2.3.

Figure 2.3: Status Register Bit Usage.

The high byte of the status register stores important system information, and can only be altered when in supervisor mode. Bits control *trace* mode, which allows single stepping among other things, supervisor or user mode, and the current level of interrupts. Interrupts and using trace are covered later in Chapter 6.

The lower byte of the status register (known as the CCR, for Condition Control Register) contains all the condition code bits, altered using arithmetic instructions, and tested for conditional jumps. Further details are given in Chapter 4. Note that there are six unused bits in the status register — these are never altered by any instructions, so you could use them for your own purposes. However, beware of getting into bad habits — other processors in the 68000 series do use these extra bits, and this applies to other non-standard techniques.

# Supervisor and User modes

When the 68008 starts up, it is in supervisor mode. What happens subsequently depends on the software that executes, and in the case of the QL the machine soon goes into user mode. Generally speaking, the QL is in user mode, though it can be persuaded to temporarily go into supervisor. When in supervisor, the processor can really do what it likes. It has access to all the memory, and the whole status register, so it can go into trace mode, and change interrupt priorities. When in user mode, the machine is restricted. The upper byte of the status register cannot be altered, though it can be read, and certain other instructions are privileged. This means that they cannot be executed when in user mode, and if you try, well, various things can happen. Basically, an exception occurs, which can trap such instructions, but I won't go too far into this at this moment.

# QL memory map

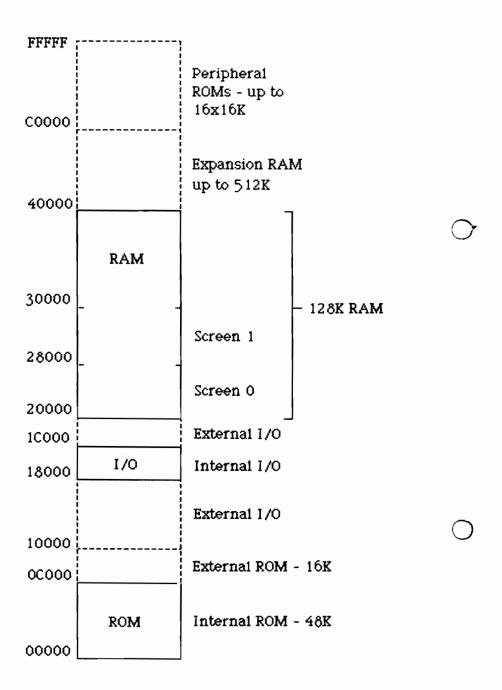

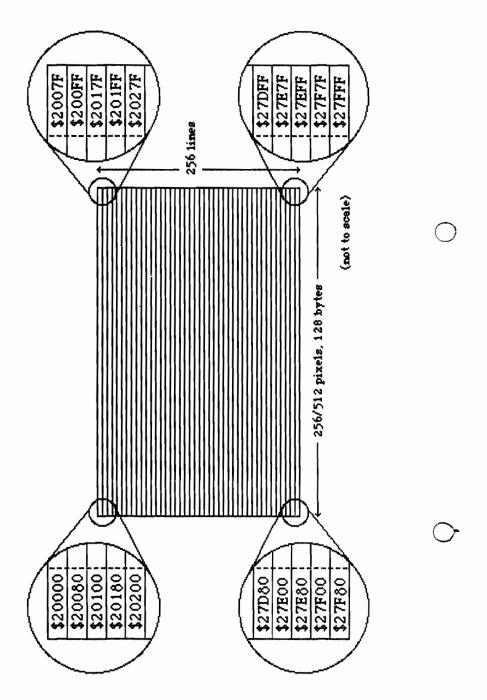

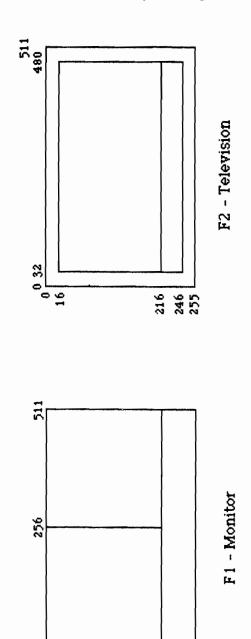

The standard QL has 128K of RAM and 48K ROM, with various other devices in its memory map. With reference to Figure 2.4, it can be seen that there are several areas that are defined but currently unused, and that out of the QL's complete address range of 1 Mbyte, there are no areas that are not defined.

# Storing machine code

With such a large amount of RAM available, you'd think that there would be loads of places in which you can store your own machine code. However, if you just put it in an area that seems to be free, sooner or later the system will use this area, wiping out your precious code. To tell the machine that you want to reserve some memory, you must use the RESPR function. RESPR stands for 'reserve procedure space', and should be followed by a number in brackets. This number is the number of bytes you wish to be made available. Unfortunately, RESPR can work

Figure 2.4: QL Physical Memory Map (not to scale).

differently on different machines, so for the moment we shall reserve space for all the routines in this book with the statement

```

a = RESPR(1024)

```

If you do this, regardless of which QL you have, 1024 bytes of memory will now be set aside for you. To find where they are, simply

#### PRINT a

which should be 261120 on a 128K RAM machine. A useful feature is that if you have a parameter of 0 in RESPR, it returns the first free location. Thus, after reserving space, RESPR(0) always tells you where your machine code may go. Unlike most other machines, on the QL there is no way of deciding first where you want your machine code to go—it will go where the system thinks it should. This means that any code you write must either be position independent, or have a special relocator. On older microprocessors, writing position-independent code is a positive nightmare, but on the 68008 it is no different to writing normal code.

Now we have a way of reserving machine code, we need a way of entering it into the machine's RAM. As the QL has no machine-code monitor, we shall have to write our own, in the form of a hex loader. Listing 2.1 below is such a program, that requires DATA statements containing hex strings to be added from line 1000 onwards. The length of the strings does not matter, so long as they are even (ie complete bytes). Line 9999 must remain, as it tells the program when there is no more data.

#### Listing 2.1: Hex Loader

```

10 DEFine FuNction dc(a$)

20 IF CODE(a$)>=CODE("a") THEN a$=CHR$(CODE(a$)-32)

30 RETurn CODE(a$)-48-7*(a$>"9")

40 END DEFine

90 a$=""

100 INPUT "Start address? ";s

105 IF s<RESPR(0) OR s>=PEEK_L(163872) THEN PRINT "WARNING:not in proper RAM":STOP

110 RESTORE 1000:READ a$

120 IF a$="" THEN GO TO 250

130 a=dc(a$(1)):IF a<0 OR a>15 THEN GO TO 200

```

```

140 b=dc(a*(2)):IF b<0 OR b>15 THEN GO T O 200

150 PRINT !a*(1 TO 2);:POKE s,a*16+b

160 s=s+1

170 IF LEN(a*)<3 THEN READ a*:GO TO 120

180 a*=a*(3 TO LEN(a*))

190 GO TO 120

200 PRINT \"Data error at location ";s

210 STOP

250 PRINT \"Last byte loaded at ";s

260 STOP

9999 DATA "":REMark end marker

```

Firstly you are asked for a starting address, which is checked to make sure that it points to RAM above RESPR (PEEK\_L(163872) calculates the top of RAM+1).

When entering machine code with this loader, either programs from this book or your own, there is an easy way to be sure that they don't work — by forgetting to reserve any memory, so RESPR(0) points not to free RAM, but to non-existent memory. Then, after you think you've POKEd your program in memory and try to execute it, the machine is very likely to fall over, losing your program.

We've now seen what is in the QL, where we can put our programs, and how we can enter them. In the next chapter, we shall start programming.

# **CHAPTER 3**

# The MOVE Instruction and Addressing Modes

The most often used instruction in the 68008's set is MOVE. It is a general 'load' instruction, and has two parameters — the source, and the destination. What it does is to take the source, whatever this is, and move it into the destination. This may sound horrendously complicated at first, but it isn't. Think of it as a LET statement in BASIC. The statement LET D0=0 has its equivalent of MOVE #0,D0. What it means exactly is 'Move 0 to register D0'. The hash is an important part of the instruction, as we shall see later. Our MOVE instruction above is not quite complete, as with all MOVEs you must specify the size of the instruction — whether you are MOVing a byte, a word, or a long word. You distinguish between them by following the MOVE with a full stop, then B, W or L, respectively. So if we want all of register D0 to be zero, the complete instruction is

#### MOVE.L#0,D0

Of course 0 is not the only number that can be moved to D0 — any number from 0 up to \$FF (for byte operations), or \$FFFF (for word), or even \$FFFFFFFF (for long word operations). There are literally thousands of different types of MOVEs, but once you know a few, the others follow — honestly! For example, a similar instruction to that above is

#### MOVE.L#0,A0

which puts zero in register A0, in exactly the same way as that above. There is a slight restriction when moving data to an address register — only word and long word sized moves are allowed — byte-sized is not. In normal programming, this is not really a problem, as byte-sized moves are seldom required.

The # in the instructions above means 'immediate addressing': think of it as 'immediately putting the data' into the register. Immediate addressing is the simplest of the twelve different addressing modes — this may

seem a lot to those of you with experience of 8 bit chips, and is one of the main reasons behind the power of the 68000 series.

# **Direct addressing**

The next addressing mode we shall look at is direct addressing. It's a nice, simple one, and is used for transferring data directly from a register. For example,

MOVE.L D3,D1

transfers whatever was in D3 into D1 (think of the comma as TO). D3 itself is not altered, so its BASIC equivalent would be LET D1=D3. Direct addressing can also be used with address registers, so 'MOVE.L A3,A0' is valid, and so is 'MOVE.L A3,D0' and 'MOVE.L D0,A3' The latter two show how you can transfer between registers regardless of type, though once again you cannot MOVE byte-sizes to or from an address register directly, so 'MOVE.B D3,A0' is not valid.

# Indirect addressing

This addressing mode can only be used with address registers, and acts like a PEEK in BASIC. For example,

MOVE.L(A0),D0

means 'move the data from location A0 to register D0', or in BASIC, LET D0=PEEK\_L(A0)

The brackets around A0 distinguish the mode from the direct mode. To compare the two, let's have a look at two apparently similar programs, and what each one does:

MOVE.L#\$28000,A0 MOVE.L#\$28000,A0 MOVE.L A0,D0 MOVE.L (A0),D0

The first instruction is the same in both programs, and puts the value of 28000 hex into register A0. The next lines look similar, but the important difference is the brackets on the one on the right. On the left, direct addressing is used to transfer the contents of A0, which we know to be \$28000, into reigster D0. On the right, it's the contents of location \$28000 that gets put in register D0. I hope you can now see the difference between direct and indirect addressing — if not, have another read.

### Post-increment addressing

This one is a natural progression from indirect addressing. It simply increments the address register after the read, by a value depending on the sige of the operation. For example,

$$MOVE.L(A0)+,D0$$

does the following: it reads the long word at location A0, puts it into D0, then increments A0. As this is a long operation, A0 gets 4 added to it. If this were a word or byte operation, it would get incremented by 2 or 1 respectively. The mode is shown by putting the address register within brackets, followed by a plus sign. It is extremely useful in many applications, including searching, filling and moving. The only 8 bit processors with this ability are also from Motorola, including the 6809.

# Pre-decrement addressing

As you may gather from the name, this is the opposite to post-increment addressing. It is similar to indirect addressing, but the register gets decremented by a value before the memory read. So,

$$MOVE.L-(A0),D0$$

would decrease A0 by four (as this is long), then read location A0 and put it in D0. As with its partner, word and byte operations produce decrements by 2 and 1, respectively. It is important to remember that the register gets decreased *before* the read, and not after as with post-increment. The clue to which one does what is in their names. The mnemonics used may help too — the minus sign comes *before* the brackets around the register.

# **Indirect with displacement**

OK, I know it's a mouthful, but you don't have to remember these official titles — as long as you remember the mnemonics, and what they do, the names aren't that important. Anyway, this is another variation on indirect addressing, this time with a number tagged on. For example,

looks at location A0+4, and places its contents in D0. The number that precedes the first bracket is the displacement, and gets added to the value of A0 before the memory is read. Note that it doesn't actually alter A0, the result of the addition being stored temporarily. The value of the

displacement can take up to 16 bits, ie from 0>65535 (or 0>\$FFFF). However, it is important to note that the displacement is taken as sign-extended, which means that 0>32767 means just that, while 32768>65535 means -32768 to -1, respectively. That is, if the displacement is greater than 32767, then you have to subtract 65536 from it. This allows negative displacements, so that

MOVE.L 65534(A0),D0

is equivalent to

MOVE.L - 2(A0),D0

which has a BASIC equivalent of LET  $D0=PEEK_L(A0-2)$ . This may seem quite complicated at first, but you should soon see the principle. If you don't, have another read, because the next one is a bit trickier!

#### Indirect with index

Most of the more complicated addressing modes are developments of simpler ones, and this is no exception. It is basically like the previous mode, but with the addition (literally) of another register. So, the instruction

MOVE.L 8(A0,D1),D0

does rather a lot. Firstly, it adds A0, D1 and the displacement — 8 in this case — all together, and stores the result temporarily. Then, it looks at that memory location, reads what's there, and puts it in D0 — wow! It's not quite that simple, though, as the displacement may only be eight bits, again sign-extended, giving a range of -128 to 127. In addition, the index register, D0 in this case, can be taken as word or long in size, and is sign-extended appropriately. Although I have used a data register as the index above, you can also use an address register, though in both cases you should specify its size, by following it with a .W or .L to suit. Thus,

MOVE.L 4(A0,A2.W),D0

has a near BASIC equivalent of LET D0=PEEK\_L(A0+A2+4). I say 'near' because it doesn't take account of any sign-extending on the displacement or index register.

Having covered nearly all the most complex modes, let's have a look at a couple of simpler ones — the absolute addressing modes.

#### Absolute addressing

There are two modes of absolute addressing — short and long. Short addressing uses a word as an address, while long addressing uses a long word. The instruction

MOVE.L \$18000,D0

is a long absolute address, as \$18000 must be a long word. What the instruction does is simply to read the contents of location 18000 hex, and place them in D0. In other words, it is equivalent to the BASIC LET D0=PEEK\_L(\$18000).

The short form is similar, but the address has to be a word, which is sign-extended so that 0-\$7FFF are as you would expect, but \$8000-\$FFFF refer to addresses \$F8000 to \$FFFFF, respectively. Unfortunately, the advantages of short addressing on the 68000 series are not really relevant to the QL, as it is very seldom indeed that you would want to examine either of these areas in this way. This is because the QL memory map does not really follow the norm for 68000 series machines. The short addressing modes were intended to access ROM routines at the bottom of the map and I/O devices at the top, but the latter are not there on the QL, while it is bad practice to do the former.

# Program counter addressing modes

A very neat feature of the 68008 is its ability to run position independent code very easily. This is inherently difficult on most 8 bit chips, with the exception again being the Motorola family.

The 68008 accomplishes this by having two special addressing modes, similar to those mentioned previously, but differing by being totally relocatable. This is done by storing not absolute addresses in the instruction, but just the displacement from the current instruction to the desired address. Thus it is possible to write programs without knowing where in the memory map they will go, as they will function anywhere. Both PC modes allow a 16 bit sign-extended displacement, allowing references forward \$7FFF bytes, and backwards \$8000 bytes — this is enough for most software. Indeed, most of the 48K ROM in the QL is totally position independent, apparently for speed and memory reasons.

There are disadvantages to PC modes though — they take longer to work out if you are hand assembling, and there are also limits on when they can be used, sometimes forcing you to use an extra instruction to do an intermediate step.

# Program counter with displacement

This is the simplest, and is similar to absolute long addressing, but is position independent. It is denoted in the mnemonic by following the address with (PC), thus

MOVE.L LABEL(PC), D0

is functionally equivalent to

MOVE.L LABEL, D0

but position independent. It will only be allowed if LABEL is not further than 32767 bytes away from the instruction.

# Program counter with index

This is vaguely similar to indirect with index, but with less parameters. For example,

MOVE.L TABLE(PC,D1.W),D0

will read the memory location TABLE+D1, and place the result in D0. As is usual for index registers, D1 in this case is sign-extended, and could be replaced by an address register, and be either word or long word in size.

#### Source and destination

In all of the above examples, the address mode under examination has been the source in the MOVE instruction, while the destination has been either a data or address register. This has been done for simplicity only, as the 68008 allows a large amount of mixing of the modes, and most of those above can also be used as destinations in MOVEs. The difference is that, instead of memory being read, it is written to. This is best illustrated by example:

| Mode           | Example           | BASIC version                 |

|----------------|-------------------|-------------------------------|

| Indirect       | MOVE.L D0,(A0)    | POKE_L(A0),D0                 |

| Post increment | MOVE.L D0,(A0)+   | $POKE_L(A0), D0: A0 = A0 + 4$ |

| Pre decrement  | MOVE.L D0,-(A0)   | $A0=A0-4$ : POKE_L(A0),D0     |

| Indirect with  |                   |                               |

| displacement   | MOVE.L D0,8(A0)   | $POKE_L(A0+8),D0$             |

| Indirect with  | MOVE.L D0,2(A0,   |                               |

| index          | D1.W),D0          | $POKE_L(A0+D1+2),D0$          |

| Absolute       | MOVE.L D0,\$28000 | POKE_L(\$28000),D0            |

As you may notice, there are a few missing from the above — firstly, immediate addressing. That's because it doesn't make sense to try something like MOVE.L A0,#\$28000 as you can't move anything to immediate data. The others missing are the two PC addressing modes, and they are missing because the 68008 hardware invisibly distinguishes between data and program, and it doesn't like to allow the alteration of program area. This is an unfortunate restriction, and is one of the reasons why extra instructions are sometimes needed when position independent code is being written.

Up to now, all the MOVEs covered have been to or from a register, and users of other processors may not be surprised by this. However, an important feature of MOVE is its ability to transfer data directly from memory to memory, without having to go via any other registers. For example, suppose you want to copy the word data from the location pointed to by A0, into the location A2+D1+6. One way of doing it is like this:

MOVE.W (A0),D0 MOVE.W D0,6(A2,D1.L)

It uses register D0 as a temporary place to store the result, and works perfectly well. However, if you want a bit more speed, and you don't want to use another register, you can combine the two by doing

MOVE.W (A0),6(A2,D1.L)

In fact, you can have any addressing mode as the source, and most addressing modes as destination, with any combination you like. The limits described above regarding destination addresses still apply though.

It is important to remember that all word and long word memory references are to *even* numbered addresses — if they are not, dire things will happen. (Later we shall see how to detect such an occurrence.) Also worth remembering is that an address register cannot directly be used as a source or destination for a byte-sized transfer.

# Word and byte-size accesses

All of the examples so far have been of long-sized MOVEs—you may be wondering what happens if you use word or byte-sizes. Well, the answer is, it depends on the destination of the MOVE. If the destination is an address register, then word-sized data will get sign-extended to 32 bits before going into the register. If it is a data register, only the lower 8 or 16 bits will be affected by the instruction, depending if it is byte or word. The

remaining bits will remain unchanged. If the destination is a memory location, then again only the appropriate number of bits will be affected.

# The first program

If you're itching to try some 68008 code, here is the first listing. Before explaining it, it's worth pointing out a few points about machine code on the QL. It is executed with the CALL command, followed by the address of the routine. You should be careful with a couple of the registers — in particular, leave A6 alone, as it is an important pointer for the system, and A7, the user stack pointer, should always be back at its original value when you have finished. To leave your machine code and get back to BASIC, the RTS instruction is used. This stands for 'Return from subroutine', and is more fully explained in a short while. Before doing the RTS though, you should always zero register D0. If you do not, you will get an error message on return to BASIC, the message depending on the value of D0.

Anyway, back to the program. It's not amazingly impressive, as it doesn't do very much, but it does serve its purpose—it's the first machine code you have done, and here it is:

#### **Listing 3.1: First Program**

| 4280 | CLR.L | DØ | zero DØ  |    |       |

|------|-------|----|----------|----|-------|

| 4E75 | RTS   |    | and back | to | BASIC |

To enter it, type in the hex pairs shown down the lefthand side, using the hex loader, and to test it try CALL RESPR(0). If all is well, you should simply get the cursor back. If not, you've managed somehow to get a four-byte program wrong!

Now is probably the best time to explain a few things about opcodes in general. It is imperative that every instruction starts at an even-numbered address. Be particularly wary of this if your program includes blocks of data in byte chunks. In addition, every instruction is an even number of bytes in length, with a minimum of two, and a maximum of ten. You will seldom find your own programs needing instructions of over six bytes in length though.

You may well be wondering how I worked out the hex for the program. There are two ways of doing it — the easy way, and the hard way. The hard way is to do it by hand, by using the codes in Chapter 8. It's not too difficult for small programs, but alterations can be difficult and it is prone to error. The easy way is to use an assembler, though at the time of writing none is available for the QL. I must admit, most of the programs in this

book I did using an assembler, though not on the QL itself — it was done on another machine, and the bytes downloaded via the RS232 port. I didn't have the assembler originally, though, so I am used to hand-coding, and I sympathise with those of you without an assembler. Even so, you can learn an awful lot more by doing it the hard way. If you've done it for other processors, and thought it was quite easy, you will have a shock when you start on the 68008, particularly regarding the number of bytes used. However, as with most things, you can soon get used to it, and your speed will usually increase.

# The stack pointer — A7

At this point it's worth having a look at the way the 68008 stack works. In fact, there are two stacks, one used when in user mode, and the other when in supervisor mode. The stack pointer is address register A7, which means that there are actually two register A7s in the processor. When you're in user mode, which is most of the time, you can only get to the user type of A7. If you're in supervisor, though, you can access both of them. For the moment, let's stick to user mode.

Where is the user stack on the QL? Well, it depends, but after a CALL it is somewhere high in memory, just below RESPR(0). As long as you don't have your 128K machine totally full, you should never run out of stack space. Like many other processor's stacks, the 68008's is 'upside down'. This means that the bottom of the stack is at a higher address than the top! Thus, when you put something on the stack, A7 decreases, and when you remove something, it increases. The value of A7 always points to the last item on the stack (always the most significant byte) which makes it very easy to manipulate it using pre-decrement and post-increment addressing. For example, if in a program you want to save the value of D1 on the stack before you do an operation, and afterwards you want to get it back, you can do this by:

MOVE.L D1,-(A7) puts it on the stack do whatever

.......

MOVE.L (A7)+,D1 then get it back

The main use for the stack is holding return addresses of subroutines, but we'll cover this later. Finally, a word of warning — it's best not to try a byte-sized operation on the stack. Although it's perfectly legal to do so (so long as it doesn't refer directly to an address register) the results will not be as expected, as it will be converted to a word operation. If the value of A7 were to become odd, it would be very dangerous, as if the system

tries to do a word or long word access subsequently using A7, such as a subroutine call or interrupt, the processor will literally stop, and your program will be lost. Therefore, as a golden rule — never do byte operations on the stack pointer.

#### Other sorts of MOVEs

There are a few other types of MOVE instruction, with widely varying uses. There are MOVEs for the condition codes, status register, user stack pointer, and the specialist instructions MOVEM, MOVEP, MOVEQ and MOVEA. I shall now cover some of these, but the remainder I shall leave for Chapter 8.

MOVEA stands for Move Address, and is the same as a normal MOVE, but with the destination being an address register. It is officially separate from the MOVE instruction, but it only confuses the matter, so you can safely ignore it. All 68000 assemblers seen so far don't require the extra A, and I don't expect any to.

MOVEQ stands for Move Quick, and is a faster (and less memory-consuming) way of doing MOVE.L#??,D0. The immediate data can be up to eight bits in length, sign-extended to a full 32 bits, giving a range of 0–127 and \$FFFFFF80 to \$FFFFFFFF. For example

#### MOVEO#12,D0

puts the long value of 12 into register D0. Note that a size isn't needed, as it is always taken to be long, and that there is no quick instruction for address registers.

MOVEM stands for Move Multiple, and is a fast and easy way of putting any number of registers into or out of memory. It is particularly useful for saving and restoring registers on the stack, and this is undoubtedly the most popular use of the instruction. For example, to save the registers D0 to D4,A0 to A3 and A6 on the stack the instruction would be

#### MOVEM.L D0-4/A0-3/A6,-(A7)

Note how the register list is specified — consecutive registers are separated by dashes, while others are separated with slashes. To save items on the stack, A7 is used in pre-decrement mode, but many other addressing modes can be used as the destination. For exact details on which ones are allowed, see Chapter 8.

To restore registers from the stack, post-increment addressing with A7 is used, and to restore the registers above the instruction would be

$$MOVEM.L(A7)+,D0-4/A0-3/A6$$

The order of the registers in the list is not important, as the actual order in which they are stacked and unstacked is determined by the processor.

# MOVE with status register

To transfer the 16 bit status register to or from another register or memory, simply put SR in either the source or destination. It is always a word instruction, due to the size of the SR. Beware though — MOVing anything TO the SR can only be done when in supervisor mode.

The 8 bit condition code register (ie the low byte of the SR) can also be specified in either the source or destination using CCR, in either user or supervisor mode. Despite its size, all such MOVEs are word-sized too, but only the lower byte is actually used.

# **CHAPTER 4**

# Condition Codes, Branching and Arithmetic

Although MOVing data about is useful, it's not really much good on its own. It is a bit like programming in SuperBASIC using just LET, without GOTO, GOSUB, IFs and DEFs, and without any maths functions at all. In this chapter we'll cover the condition codes, branches, jumps, and subroutines. Towards the end, we'll also come across the various arithmetic operations.

#### The condition codes

The condition codes are stored in the lowest five bits of the status register, and cover five types of condition, namely X (extend), N (negative), Z (zero), V (overflow), and C (carry). I'll deal with these one by one, but not in that order. Firstly let's look at an instruction that is one of the most common that alters them — subtract.

#### The SUB instruction

This stands for subtract, and is used for subtraction involving data registers. There are several forms, but let's start by looking at the instruction

SUB.L#8,D0

Notice that, as with MOVE, a size has to be specified, and in this case it is long. What this means is 'subtract 8 from the contents of D0', ie do the calculation D0=D0-8. The instruction doesn't just do the subtraction, but it looks at the result and alters the condition codes suitably. There are five condition codes, and we'll deal with each of them in turn, starting with the easiest.

#### Z — Zero flag

This is the simplest condition, and is self-explanatory. If the result is zero, then this condition flag is set, else it is reset. Thus, in the above example, the Z flag will be set only if D0 equalled 8 originally — if it equalled anything else, it will be reset.

#### C — Carry flag

The carry flag is set if the subtraction 'carries through zero'. Thus, if D0 was 7, and had 8 subtracted from it, the result would be -1, and the carry generated because the result does 'carry through zero'. If it was between 8 and 0 inclusive, no carry would be generated.

#### N — Negative flag

This flag is set if the result is 'negative'. As we are talking about two's-complemented numbers, negative means if the most significant bit is set. So for long operations, a result is negative if bit 31 is set, else it is positive. For word results, bit 15 determines its sign, and byte results use bit 7 as the sign bit. Thus in the above example, the N bit will be set if the result has bit 31 set, ie lies in the range \$FFFFFFFF to \$80000000 inclusive. So, if D0 was 100 the result of the subtraction would be -2 which is \$FFFFFFFE, which is negative, so N would be set.

#### V — Overflow flag

The overflow flag is set after an operation if the result is 'too big' for the specified size, and will be set if the sign changes after a calculation when it shouldn't. For example, if you did SUB.B #8,D0 and D0 was originally -125, the proper answer would be -133, but this is too big for 8 bits, and the result would end up as 123, which is positive. As the sign changed when it shouldn't have, an overflow would be generated.

# X — Extend flag

This is effected by certain operations only, and is set the same as the carry flag. It is a 'special' carry flag, used in multi-precision operations, such as floating point arithmetic. It is set to the same state as the carry flag by a Subtract.

The previous example used a long-sized subtract — if word or byte sizes are used, only the relevant part of the operands is read and altered so

SUB.B#9,D0

would set the Z flag if D0=9, or if the least significant byte is D0, so it would also be set if D0=\$1009, or \$F1234E09 for that matter.

#### **Branches**

No, this has nothing to do with trees. A branch is a type of jump, like a GOTO in BASIC. There are no less than 15 different branch instructions, referred to generally as Bcc (for Branch on Condition Code). The simplest is BRA, which stands for Branch Always, and should be

followed by a program label. When executed, it means 'transfers control to whichever location the label is', so an instruction

#### **BRA START**

would cause a jump to whatever location START is. There is a restriction on all branches though — they can only be to locations within 32767 bytes of the instruction. There are eight other straightforward branch instructions, namely

| BEQ | branch if equal (Z)              |

|-----|----------------------------------|

| BNE | branch if not equal (not Z)      |

| BCS | branch if carry set (C)          |

| BCC | branch if carry clear (not C)    |

| BMI | branch if minus (N)              |

| BPL | branch if plus (not N)           |

| BVS | branch if overflow set (V)       |

| BVC | branch if overflow clear (not V) |

|     |                                  |

As can be seen by the mnemonics, these eight are directly related to the four condition codes. Note that there are no conditional branches on the extend flag. There are some more types of branches, but they are not really applicable to SUB, only CMP, which we'll see later.

There is another way of branching — using the JMP instruction, which stands for Jump. It can be followed not just by an address, like Bcc, but by several different addressing modes, though its use in your own programs is limited on the QL as it is not normally position independent.

## Other types of SUB

The usual SUB instruction has one of two general forms — either

SUB (address), Dx

or

SUB Dx, (address)

The first type includes the above examples, and subtracts the contents of (address) from the data register. The second type does a similar subtraction, but the other way round, in other words it subtracts the value of the data register from the contents of the address, then puts the result back in the address. To help remember which is which, think of the

comma as 'from'. Here are some examples, with their BASIC equivalents:

SUB.B (A1),D1 D1=D1-PEEK(A1)

SUB.L \$28000,D4 D4=D4-PEEK\_L(\$28000)

SUB.W D4,6(A1) POKE\_W A1+6, PEEK\_W(A1+6)-D4

Another type of subtraction is SUBA, for subtracting values from address registers. It has the general form

SUBA (address), Ax

This cannot be byte-sized, and there is no equivalent for SUB Ax, (address), though. There are other differences too. The condition codes are not altered a scrap by SUBA and, with a word-sized SUBA, both parameters are sign-extended to 32 bits. Another type of subtraction is SUBI, for Subtract Immediate, and it has the general form

SUBI #(data),(address)

It subtracts the immediate data from the contents of the address, as you would expect. The final form of SUB is SUBQ, for Subtract Quick, of the form

SUBQ #(data),(address)

It is similar to SUBI, but very much faster and less memory-consuming. The data can only be from 1 to 8 inclusive, though. The way an instruction, like SUB, can have different forms is repeated for several other instructions, and a good assembler should automatically distinguish between them.

#### The CMP instruction

This stands for 'compare', and is used, not surprisingly, for comparing things with data registers. It has the general form

CMP (address), Dn

where (address) can be any of the modes described in the previous chapter, without restriction. There are many different types of CMP and,

like MOVE, it has to have a size — byte, word or long, denoted by the usual .B, .W or .L following the CMP. For example, the instruction

CMP.L #8,D0

'compares' 8 with D0. What the processor does is to subtract the (address) from the data register, but not store the result anywhere. Although the result is not stored, the values of the condition code register are affected, depending on the result of the subtraction. So, with the above instruction, the processor does the subtraction

'contents of D0'-8

## Other compare instructions

The normal CMP instruction compares a parameter with a data register. There is a similar instruction CMPA, which compares a parameter with an address register. Note that CMPA cannot have byte-sized operations, and that word-sized CMPAs are sign-extended to 32 bits before the operation.

There is another compare instruction, namely CMPI, which stands for 'compare immediate'. It has the general form

CMPI #data,(address)

and can be byte, word or long in size. The size of the immediate data is always the same as the size of the instruction, (address) can be most of the different addressing modes, with the exceptions of address register direct, both PC modes, and immediate mode. Thus these are invalid:

CMPI.L#5,A0 can be replaced by CMPA.L#5,A0 CMPI.L#7,TYPE(PC)

CMPI.L#9,#6 doesn't make sense!

## More branching

As well as the conditions described previously, there are some additional ones usually only useful after a CMP instruction. They do not act directly on each condition code bit, but use combinations to produce useful extra conditions. Firstly, there are two that use combinations of the carry and zero flag, namely

BHI branch if higher

BLS branch if lower or same

So, after the instruction

CMP.B #20,D0

a BHI would be executed if D0 was HIgher than 20, ie 21 to 255 inclusive, and a BLS executed if it was Lower or the Same, ie 0 to 20 inclusive.

As well as these conditions, there are six others, which work on signed values:

| BGT | branch if greater than |

|-----|------------------------|

|-----|------------------------|

BGE branch if greater than or equal to

BLT branch if less than

BLE branch if less than or equal to

These do not use single bits of the condition code register, or even pairs, but combinations of the N, V and Z flags, to produce these extra conditions. Don't confuse 'less than' with 'lower' — the former takes into account the signs of the operands, while the latter takes absolute values.

## An example — converting to ASCII

It is often necessary to convert a number in a register, ranging from 0 to 15, into an ASCII digit, from 0 to F. The problem is made clearer by examining the ASCII codes corresponding to each possible value:

| Number                    | 0            | 1             | 2             | 3             | 4             | 5             | 6             | 7  | 8  |

|---------------------------|--------------|---------------|---------------|---------------|---------------|---------------|---------------|----|----|

| Symbol                    | 0            | 1             | 2             | 3             | 4             | 5             | 6             | 7  | 8  |

| ASCII                     | 48           | 49            | 50            | 51            | 52            | 53            | 54            | 55 | 56 |

| Number<br>Symbol<br>ASCII | 9<br>9<br>57 | 10<br>A<br>65 | 11<br>B<br>66 | 12<br>C<br>67 | 13<br>D<br>68 | 14<br>E<br>69 | 15<br>F<br>70 |    |    |

The conversion looks easy up to 9 — simply add 48 on to the number. However, after 9 there is a jump in the ASCII equivalent of 7, then it gets back into step. What's required is thus:

If the number is >9 then add 7 to it Add 48 (=ASCII for 0)

To code this in 68008, it has to be decided which register should hold the number. For convenience I chose to use D1 (choosing an address register would make life very much more difficult — try it if you like). The section of code to do the above turns out to be

CMP.B #9,D1

BLS DONTADD

ADDQ.B #7,D1

DONTADD ADD.B #"0",D1

Do you see the way the BLS works out whether or not to add the extra 7? The 'add 7' is skipped over if D1 is less than or the same as 9. This is not a complete piece of code on its own, so I've given no hex to enter into the QL. It is used in a short while though, to print out numbers in hex.

## How they are calculated

Don't read this unless you want to, but I've included it for reference. Don't bother even thinking of learning this — it would be very difficult, and in any case there is absolutely no point. The table shows just what combinations of condition codes produce the extra conditions.

#### Condition

HI C=0 AND Z=0

LS C=1 OR Z=1

GT (N=1 AND V=1 AND Z=0) OR (N=0 AND V=0 AND Z=0)

GE (N=1 AND V=1) OR (N=0 AND V=0)

LT (N=1 AND V=0) OR (N=0 AND V=1)

LE (Z=1) OR (N=1 AND V=0) OR (N=0 AND V=1)

## **Looping using DBcc**

This is a very useful instruction for creating loops, using a data register as a counter. The 'cc' refers to a condition, and it has to be followed by a data register, then a label. The conditions allowed are the 14 described previously, together with two additional instructions — T for True, and F for False. The most common form of the instruction is

#### DBF D0,LOOP

What this means is 'decrement D0 and branch until False or until D0=-1'. As the condition false can never be met, this translates to 'decrement D0 and branch until D0=-1', so it is ideal for doing something a set number of times. As the loop finishes when the counter reaches -1, the initial value of the counter should be one less than the number of times round the loop. As an example, there follows a program that scrolls the screen up one line. To do this, the section of memory from \$20080 to \$27FFF has to be moved back in memory \$80 bytes, and DBF is ideal for this.

#### **Listing 4.1: Screen Scroll**

| 3 <b>0</b> 3C7F7F | MOVE.W | #\$7F7F,DØ    | set count       |

|-------------------|--------|---------------|-----------------|

| 207C0002          | MOVE.L | #\$20080,A0   | first location  |

| ØØ8Ø              |        |               |                 |

| 1150FF80 LOOP     | MOVE.B | (AØ),-128(AØ) | move a byte     |

| 5288              | ADDO.L | #1,AØ         | increment AØ    |

| 51C8FFF8          | DBF    | DØ,LOOP       | do whole screen |

| 7000              | MOVEO  | #Ø,DØ         | ready for BASIC |

| 4E75              | RTS    |               | and exit        |

A total of \$7F80 bytes have to be moved, so this value less 1 is put into the count register, D0. (A word MOVE can be used, as DBcc only decrements the lowest 16 bits of the data register, and the test for -1 is also only done on the lower word.) The initial value of \$20080 is put into register A0, and then the MOVE instruction does the job of moving the byte back in memory. It uses indirect addressing for the source, and indirect addressing with displacement for the destination. The detail of the next instruction, ADDQ, will be explained later, but for now just take it as read that it adds 1 to A0. The next instruction is the DBF, which does the hard work of decrementing D0, and going to LOOP until D0=-1, when it returns back to BASIC.

Although False is the usual condition in DBcc instructions, any of the others can be used. If the condition is met, then the loop will be exited prematurely, and the data register will not be decremented at that time. It makes no sense to use DBT, as the condition will always be met (as it is True), and will have no effect. (It is useful to know that some assemblers can accept DBRA as an alternative for DBF.)

#### Subroutines

There are two ways of calling subroutines on the 68008, both using a similar idea. They are JSR, for 'Jump to Subroutine', and BSR, for 'Branch to Subroutine'. When executed, the address following the instruction is put on the current stack, and the desired routine jumped to. For example,

When the BSR gets executed, the value of REST is put on the stack, then control will pass to location PRINT. When the routine PRINT has finished, it returns to location REST with the instruction RTS — return from subroutine. This is the same RTS we use to get back to BASIC after a CALL, as the code you execute with a BASIC CALL instruction is just another subroutine to the system. What RTS does is to remove the top item from the stack, then pass control to it.

BSR, as with the other branch instructions, can only refer to locations within 32767 bytes. For longer subroutine calls, JSR has to be used, which can be followed by one of many addressing modes. The standard form is

#### **JSR ROUTINE**

where ROUTINE is expressed using absolute long addressing, but this form is not position independent, as BSR is. Many addressing modes can be used in a JSR instruction, though there are limitations. For full details, see the relevant page in Chapter 8.

#### The CLR instruction

This stands for 'clear', and is a fast and memory-efficient way of zeroing registers and memory. It can be byte, word or long in size, and the number of bits zeroed correspond to the size of the operation. Most of the addressing modes can be used to indicate what requires zeroing, and some are shown:

CLR.B D0 clear lowest 8 bits of register D0 clear lowest 16 bits of location A1 clear 32 bits at location FLAG

The forbidden addressing modes are address direct (so CLR.L A0 is not allowed), both PC modes, and immediate mode. As has been mentioned, register D0 must be 0 on return from BASIC, and the fastest way to do this is with the instruction CLR.L D0 which has an opcode of \$4280.

#### More arithmetic

We have covered SUB and CMP, and their associated forms, and there is one more main arithmetic instruction left — that of ADD.

#### The ADD instruction

There are no prizes for guessing what this one does! It adds something to something else, the 'somethings' depending on the type of ADD. The types, along with their general forms are:

ADD (address),Dx add contents of address to register ADD Dx,(address) add register to contents of address ADDA (address),Ax add contents of address to register ADDI#(data),(address) add data to contents of address fast form of ADDI

The range of additional types of ADD is similar to those for SUB, with similar rules, namely:

ADDA cannot be byte-sized, does not affect the condition codes, and always sign-extends its parameters to 32 bits; and ADDQ can only add the values 1 to 8 inclusive. The condition codes are affected in the usual way (except ADDA), though overflow is caused slightly differently — an overflow in ADD is caused by a sign-change when it shouldn't, eg ADD.B #8,D0 if D0=125, the result is 133, which is correct, but the sign has changed — it can be thought of as -123 as bit 7 is set.

## Logical operations

There are three main logical operations — AND, OR, and Exclusive-OR, which share a similar set of instructions.

## The AND operation

A logical AND takes the bits of two numbers, then ANDs them together. It is equivalent to the && operation in SuperBASIC. There are two general forms of the instruction:

AND (address), Dx and AND Dx, (address)

The first takes the contents of the address, logically ANDs it with the data register, and puts the result back into the data register. It can be any size, and only the relevant number of bits of each parameter are used.

The second form is similar, but the result of the operation is put back into the address. Here are some examples:

AND.B #\$0F,D1 D1=D1&&15 AND.W D3.RESULT POKE W

RESULT, PEEK\_W(RESULT) & & D3

There is another sort of AND, that of ANDI, for And Immediate. It has the form

ANDI #(data),(address)

and its main use is to logically AND memory with immediate data. The size of the data matches the size of the instruction. A good assembler will automatically decide which type of AND is necessary.

The final two types of AND are to alter the status register:

ANDI#(data),CCR and ANDI#(data),SR

The first has a data size of eight bits, and ANDs the data with the condition codes, placing the result back into the CCR. The second has a data size of 16 bits, and ANDs it with the contents of the complete status register, placing the result back in the SR. This is a privileged instruction, because of its potential power, and will only execute in supervisor mode.

#### **OR and EOR instructions**

The OR instruction does a similar operation to the SuperBASIC  $\mid \mid$  function. If either bit in the two numbers is set, then the resultant bit will be set, else it will be reset. The EOR instruction (for Exclusive OR) does a similar operation to  $\mid \mid$  in SuperBASIC. If both bits in a number are 1, then the resultant bit will be 0, or if one bit is 1, the result will be 1. There is a similar range of these functions to AND, namely

OR (address),Dx

OR Dx,(address)

ORI #(data),(address)

ORI #(data),CCR

ORI #(data),SR (privileged instruction)

EOR Dx,(address)

EORI#(data),(address)

EORI#(data),CCR

EORI#(data),SR (privileged instruction)

Note that there is one missing though — EOR (address), Dx is not permitted. You have to use an intermediate data register, eg

MOVE.B MASKS,D0 EOR.B D0,D2

instead of

EOR.B MASKS, D2

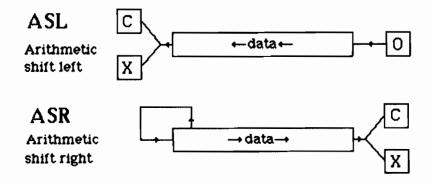

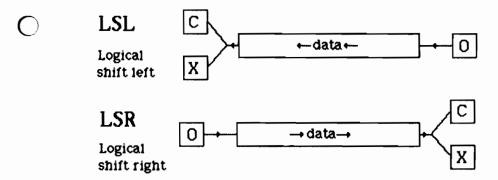

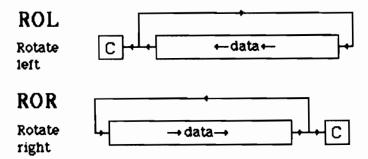

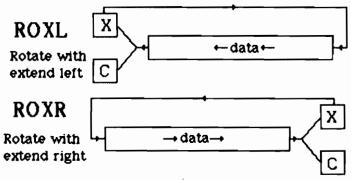

#### Shifts and rotates

The 68008 has four types of shifts and rotates, all in both directions, and they are:

LSR logical shift right LSL logical shift left

ASR arithmetic shift right ASL arithmetic shift left

ROR rotate right ROL rotate left

ROXR rotate with extend right rotate with extend left

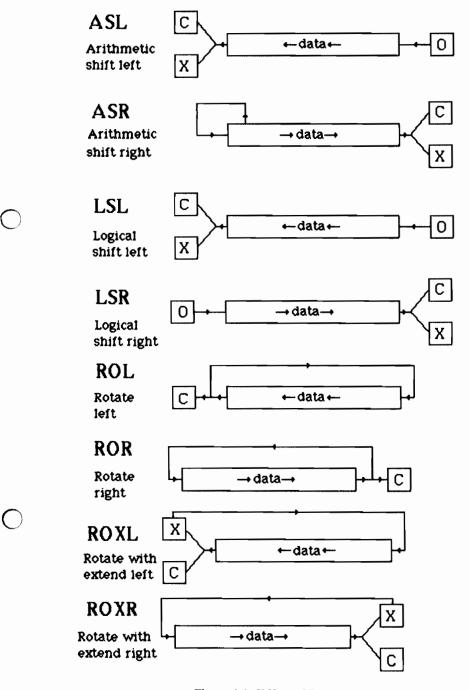

What they do is move all the bits of an operand in a certain direction, though the exact details depend on the instruction type, best illustrated by a diagram (see **Figure 4.1**).

With all of these, any size can be specified, and only the expected number of bits are affected. The way in which the number of rotations can be specified, and what parameter is operated on, does vary, depending on the operation. These methods are the same for all the instructions, but in these examples ASL is used:

ASL Dx, Dy may be byte, word or long, and the number of times register Dy is shifted depends on the contents of register Dx, MOD 64).

ASL #(data), Dx may be byte, word or long, the number of shifts determined by immediate data, from 1 to 8 inclusive. Register Dx is the operand shifted.

ASL (address) this can be word only, and the contents of the address are only shifted once.

Arithmetic shifting is most used for signed numbers, and logical shifting for unsigned numbers. Rotate with extend is mainly used for high-precision maths operations.

The limit of eight on the number of operations when specified with immediate data is a nuisance, and there are two ways of getting around it. You can either put the count in another data register, or do an immediate count version a couple of times. For example, supposing you wanted to logically shift D3 word 12 times to the right, you could do either

MOVE.B#12,D0

LSR.W D0,D3 using D0 as the count

or

LSR.W #8,D3 maximum allowed

LSR.W #4,D3 then do again, giving a total of 12

The former method is preferable for large counts, while the latter is useful if register usage is limited, and there is no spare data register.

Figure 4.1: Shifts and Rotates.

## Printing in hex

As a useful exercise, there follows a program that uses many of the instructions we've come across so far — a routine to print the value of a register in hex, though the actual mechanics for getting a character on the screen have not yet been covered.

Firstly, let's think about what is involved. We have to take each nibble (four bits), starting at the most significant, convert it to a single ASCII digit from 0 to F, print it, then do the same for all eight nibbles, printing the complete hex value. Converting a register value of 0 to 15 into an ASCII value of 0 to F has already been covered, so the main parts to be done are the 'extracting the nibble', and counting for eight digits. The complete subroutine looks like this:

#### **Listing 4.2: Hex Printing**

```

prints value of D1 as 8 digit hex

MOVEQ

7007

HEX8

#7,DØ

set count

E999

LOOP

ROL.L

#4,D1

rotate nibble

2FØ1

MOVE.L D1,~(A7)

save D1 on stack

#$ØF,D1

Ø201000F

AND.B

D1=0 to 15

ØCØ1ØØØ9

CMP.B

#9,D1

convert to ASCII

BLE

DIGIT

6FØ2

ADDQ.B #7,D1

5EØ1

ADD.B #"0",D1

06010030 DIGIT

PRINT

6108

BSR

print the character

221F

MOVE.L (A7)+,D1

restore D1

51C8FFE6

DBF

DØ,LOOP

do all digits

and finish

4E75

RTS

prints chr$(d1) onto screen

without corrupting any registers

(Don't worry how it does it yet)

10 U C. . .

48E7DØCØ PRINT

MOVEM.L DØ-1/D3/AØ-1,-(A7)

20700001

MOVEA.L #$00010001,A0

0001

76FF

MOVEQ

#-1,D3

MOVEQ #5,DØ

7005

4E43

TRAP

#3

4CDFØ3ØB

MOVEM.L (A7)+,DØ-1/D3/AØ-1

4E75

end of subroutine

```

It starts off by assuming the register value to be printed lies in D1. Register D0 is going to be the counter, so it gets initialised to the number of digits -1, which is 7. (The minus one is necessary because we're going to use DBF.) We then enter the loop, in which D1 (long) is rotated left four times. To start with, this puts the highest nibble (at bits 28–31) into the lowest four bits, and rotates everything else in the register up one nibble. The MOVE saves the value of D1 on the stack for later, then the AND makes D1 hold 0 to \$0F inclusive, which then gets converted to its ASCII equivalent. (This corrupts the value of D1, which is why we saved it previously.)

After the conversion, the BSR PRINT calls the subroutine that sends character D1 to the screen, then D1 gets restored to its old value, and the DBF makes sure the loop goes round eight times. Each time, the next nibble gets rotated around into the lowest four bits, converted and printed, until the whole number has been printed. Don't concern yourself with PRINT for the moment — it is fully covered in Chapter 7, but take it as read that it sends a character to the screen, without corrupting any registers.

The subroutine itself cannot be used directly from BASIC as it stands — it will work perfectly, but generates an error message when it finishes, because the final value of D0 will be -1. It is intended to be called by other bits of program, so D0 is not explicitly cleared.

It can be extended to print values in hex of 8 or 16 bit quantities too. For 8 bit data, with two hex digits, the initial value of D0 has to be set to 1, and D1 rotated initially so what was originally in the lowest four bits goes into the highest. For 16 bit data, D0 has to be 3 to start with, and its low and high words swapped around for the data to be in the right place. This can be done quickly with the SWAP instruction. The necessary extra instructions are:

Listing 4.3: Printing 8 and 16 Bit Values

(must immediately precede Listing 4.2)

|                              |      | 8-bit                         | data – 2 hex digits          |                                                           |  |

|------------------------------|------|-------------------------------|------------------------------|-----------------------------------------------------------|--|

| 7001<br>E099<br>6008         | HEX2 | MOVEQ<br>ROR.L<br>BRA         | #1,D0<br>#8,D1<br>LOOP       | set count<br>rotate value<br>and print it                 |  |

|                              |      | 16-bit                        | data - 4 hex digits          |                                                           |  |

| 7003<br>4841<br>6002<br>7007 | HEX4 | MOVEQ<br>SWAP<br>BRA<br>MOVEQ | #3,DØ<br>D1<br>LOOP<br>#7,DØ | set count<br>move data<br>and print it<br>rest of routine |  |

|                              |      | ******                        |                              |                                                           |  |

|                              |      |                               |                              |                                                           |  |

(The hex bytes assume that the previous routine directly follows these instructions.) This now gives three subroutines for the price of one. They are HEX2, for 8 bit values, HEX4, for 16 bits, and HEX8, for 32 bits. Having done this you could always try for something a little more adventurous — how about printing them in decimal? (This is very tricky indeed, and the faint-hearted shouldn't try it — anyway there's a nice QDOS routine that does it all for you in the ROM!)

#### CHAPTER 5

## Further Instructions and Passing Parameters

One of the instructions carried over from previous Motorola processors is LEA, which stands for 'Load Effective Address'. At first sight it seems identical to the MOVEA instruction, but there is a subtle difference, best illustrated by this example:

MOVE.L LABEL(PC),A1

LEA LABEL(PC),A1

What the MOVE does is to read the *contents* of location LABEL, and put them in register A1. The similar LEA instruction places the *value* of LABEL into A1, not the contents of the location. The difference between these two is a well-known source of confusion to newcomers to the 68000 series, which is understandable. LEA is like MOVE, but the value of the address is placed in the selected address register. To get the same effect as the above LEA instruction, you could do

#### MOVE.L#LABEL,A1

but there is an important difference. The LEA form, as it uses PC mode, is position independent, whereas the MOVEA form, using direct addressing, is not.

Probably the main use of LEA is in getting around the restriction that prevents PC mode being used as the destination in MOVE instructions. For example, suppose you wanted to do

MOVE.L D3,STORAGE(PC)

which is not allowed, you could get around the restriction with

LEA STORAGE(PC),A1 MOVE.L D3,(A1)

The LEA sets A1 to the value of STORAGE (using PC mode), and then the MOVE does the transferring of data. LEA can also be used to add

things together faster than can be done with the ADD instruction. For example, suppose you wanted to calculate the sum of A1,A2 and 9 and put the result in A3, it could be done with

MOVE.L A1,A3 A3=A1 ADDA.L A2,A3 A3=A1+A2 ADDA.L#9,A3 A3=A1+A2+9