# **BCD COUNTER/4-BIT LATCH/BCD DECODER/DRIVER**

BULLETIN NO. DL-S 7211719, MAY 1972~REVISED DECEMBER 1972

#### **FUNCTION TABLE**

| IN                     | PUTS  |                 | OUT | PUTS             |

|------------------------|-------|-----------------|-----|------------------|

| COUNT PULSE<br>(CLOCK) | CLEAR | LATCH<br>STROBE | ON† | $\bar{\alpha}_D$ |

| Х                      | L     | L               | 0   | н                |

| 1                      | н     | L               | 1   | Н                |

| 2                      | н     | L               | 2   | н                |

| 3                      | н     | L               | 3   | н                |

| 4                      | H     | L,              | 4   | Н                |

| 5                      | н     | L               | 5   | н                |

| 6                      | н     | L               | 6   | н                |

| 7                      | н     | L               | 7   | н                |

| 8                      | H     | L               | 8   | L                |

| 9                      | • н   | L               | 9   | L                |

| 10                     | н     | L               | 0   | н                |

| 11                     | н     | н               | 0   | н                |

| SN74142 | · · · | JO | RN | PΑ | CKA | ١GE |

|---------|-------|----|----|----|-----|-----|

|         | (TO   | PV | EW | )  |     |     |

| CLR  | 1 | $\cup_{16}$ | Ľ | Vcc                             |

|------|---|-------------|---|---------------------------------|

| 7[   | 2 | 15          |   | CLK                             |

| 6□   | 3 | 14          |   | $\bar{\mathbf{q}}_{\mathbf{D}}$ |

| 4[   | 4 | 13          |   | STRE                            |

| 5 🗆  | 5 | 12          |   | 9                               |

| 3□   | 6 | 11          |   | 8                               |

| 2[   | 7 | 10          |   | 0                               |

| GND□ | 8 | 9           | D | 1                               |

### description

The SN74142 contains a divide-by-ten (BCD) counter, a four-bit latch, and a decoder/Nixie‡ tube driver on a monolithic chip and is packaged in popular 16-pin packages. This single MSI function can replace the equivalent of three separately packaged MSI circuits to reduce printed-circuit board area and the number of system interconnections, resulting in reduced costs and improved reliability.

Four master-slave flip-flops are fully decoded to provide a divide-by-ten counter. A direct clear input will, when taken low, reset and hold the counter at zero (all Q outputs low, QD output high). While the clear input is inactive (high), each positive-going transition of the clock will increment the counter. The  $\overline{\mathtt{Q}}_{\mathsf{D}}$  output is made available externally for cascading to n-bit counters.

The Q outputs of the counter are routed to the data inputs of the four-bit latch. While the latch strobe input is low, the internal latch outputs will follow the respective Q outputs of the counter. When the latch strobe input is taken high, the latch stores the data which has been setup by the counter outputs prior to the low-to-high level transition of the latch strobe input. The  $\bar{\Omega}_{\mathsf{D}}$  output from the counter is not stored by the latch since it is intended for clocking the next counter stage. This means that the system counter can continuously acquire new data. Since all outputs of the latch and Q outputs of the counter drive low-capacitance on-chip loads, the circuitry is considerably simplified with respect to the number of components required. This results in a highly efficient function which typically reduces power requirements 15% when compared to systems using the three separate packages.

The SN74142 counter/latch/driver features fully buffered inputs to reduce drive requirements to one normalized Series 74 load per input, and diode-clamping of all inputs to minimize transmission line effects. The counter will accept input clock frequencies up to 20 MHz and is entirely compatible for use with all popular TTL and DTL logic circuits. The high-performance n-p-n driver outputs are identical to the SN74141 and have a maximum off-state reverse current of 50 microamperes at 55 volts.

<sup>&</sup>lt;sup>†</sup>All other outputs are off.

H = high level, L = low level, X = irrelevant

$<sup>{}^\</sup>ddagger \! Ni\! xie$  is a registered trademark of the Burroughs Corporation.

| Supply voltage, VCC (see Note 1) .      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |     |     | ,    | 7 V               |   |

|-----------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|-----|-----|------|-------------------|---|

| Input voltage                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |     |     | . 5  | .5 V              |   |

| Off-state current into outputs 0 thru 9 | • | • | • | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |     |     | . 1  | mA                |   |

| Operating free-air temperature range    |   | • | • | • | • | • | • | • | • | • | • | • | • | • |   | • | • | • | • | • | • |   |   |   |   |    | Ċ   | ı°C | to . | 70°C              | : |

| Operating free-air temperature range    | ٠ | • | ٠ | • | • | • | • | • | ٠ | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | • | • | • | ٠, | :=0 | C+. | 11   | eu <sub>o</sub> c |   |

| Storage temperature range               |   |   |   |   |   |   |   |   |   | ٠ |   | ٠ |   | ٠ |   | • | ٠ | ٠ | • | • | ٠ | • | • | • |   | -6 | ,:, | CI  | , ,, | JU C              | ′ |

NOTE 1: All voltage values are with respect to the network ground terminal.

### recommended operating conditions

|                                                                                                                         |                  | MIN  | MOM | MAX              | UNIT                  |

|-------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|------------------|-----------------------|

| Supply voltage, VCC                                                                                                     |                  | 4.75 | 5   | 5.25             | V                     |

| High-level output current from QD, IOH                                                                                  |                  | 1    |     | -400             | μΑ                    |

| Low-level output current from Qp, IQL                                                                                   |                  |      |     | 8                | mA                    |

|                                                                                                                         |                  | 0    |     | 20               | MHz                   |

| Input clock frequency, fclock  Clock pulse width, tw(clock) (see Figure 1)  Clear pulse width, tw(clear) (see Figure 1) | High logic level | 15   |     |                  |                       |

|                                                                                                                         | Low logic level  | 35   |     |                  | 115                   |

| Clear pulse width, tw/clear) (see Figure 1)                                                                             |                  | 25   |     |                  | ns                    |

| Strobe pulse width, tw(strobe) (see Figure 1)                                                                           |                  | 20   |     |                  | 5 V 0                 |

| Clear inactive-state setup time, t <sub>SU</sub> (see Figure 1)                                                         |                  | 25   |     |                  | ns                    |

| Strobe time, 1 <sub>Strobe</sub> (see Figure 1)                                                                         |                  | 45   | -   | tw(clock)<br>+10 | ns                    |

| Operating free-air temperature, TA                                                                                      |                  | 0    |     | 70               | MHz ns ns ns ns ns ns |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|            | PARAMETER                              | TEST CONDITIONS†                                 | MIN | TYP‡     | MAX  | UNIT |

|------------|----------------------------------------|--------------------------------------------------|-----|----------|------|------|

| VIH        | High-level input voltage               |                                                  | 2   |          |      | ٧    |

| VIL        | Low-level input voltage                |                                                  |     |          | 0.8  | V    |

| VIK        | Input clamp voltage                    | V <sub>CC</sub> = M1N, 1 <sub>I</sub> = -12 mA   |     |          | 1.5  | ٧    |

| VOH        | High-level QD output voltage           | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -400 μA | 2.4 | 3.4      |      | ٧    |

| VOL        | Low-level QD output voltage            | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 8 mA    |     | 0.2      | 0.4  | ٧    |

| VO(on)     | On-state voltage, outputs 0 thru 9     | V <sub>CC</sub> = MIN, I <sub>O</sub> = 7 mA     |     |          | 2.5  | ٧    |

| VO(off)    | Off-state voltage, outputs 0 thru 9    | V <sub>CC</sub> = MAX, I <sub>O</sub> = 0.5 mA   | 60  |          |      | V    |

| (O(off)    | Off-state current, outputs 0 thru 9    | V <sub>CC</sub> = MAX, V <sub>O</sub> = 55 V     |     |          | 50   | μА   |

| 11         | Input current at maximum input voltage | V <sub>CC</sub> = MAX, V <sub>1</sub> = 5.5 V    |     |          | 1    | mA   |

| ЧН         | High-level input current               | VCC = MAX, V1 = 2.4 V                            |     | <u> </u> | 40   | μΑ   |

|            | Low-level input current                | VCC = MAX, VI = 0.4 V                            |     |          | -1.6 | mA   |

| llL.       | Short-circuit QD output current        | V <sub>CC</sub> = MAX                            | -18 |          | -55  | mA   |

| los<br>lcc | Supply current                         | VCC = MAX, All outputs open                      |     | 68       | 102  | mA   |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

### switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ} \text{C}$

|                  | PARAMETER                                                       | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------------------------------|-------------------------|-----|-----|-----|------|

| tPLH             | Propagation delay time, low-to-high-level  Op output from clock | C <sub>1</sub> = 15 pF, |     | 35  | 55  | ns   |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level  QD output from clock | R <sub>L</sub> ≈ 800 Ω, |     | 30  | 45  | 113  |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level  Op output from clear | See Figure 1            |     | 30  | 45  | ns   |

2

$<sup>\</sup>ddagger$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $\top_A = 25 ^{\circ} \text{C}$ .

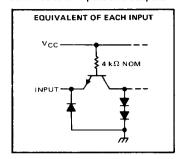

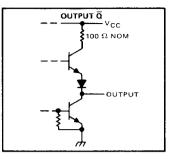

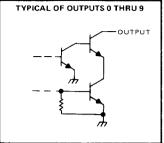

### schematics of inputs and outputs

Resistor values shown are nominal.

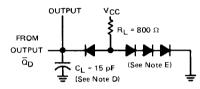

### PARAMETER MEASUREMENT INFORMATION

#### LOAD CIRCUIT

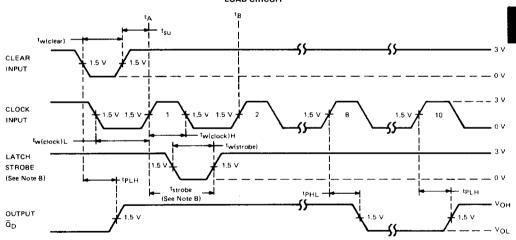

- VOLTAGE WAVEFORMS

NOTES: A. This typical abbreviated sequence illustrates clearing from count 8 or 9 and counting through ten clock pulses. Clock pulses 3 through 7 and 9 are omitted for brevity.

- B. Strobe input can go low at any time; however, the positive transition to store data from any given clock transition  $(t_A)$  must occur a minimum of 45 ns after  $t_A$  and prior to 10 ns after the next positive-going clock transition  $(t_B + 10 \text{ ns})$ .

- C. Input pulses are supplied by generators having the following characteristics:  $t_r \le 7$  ns,  $t_f \le 7$  ns, PRR = 1 MHz, and  $Z_{OUT} \approx 50 \ \Omega$ .

- D. C<sub>L</sub> includes probe and jig capacitance.

- E. All diodes are 1N3064 or equivalent.

FIGURE 1

## This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.